Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

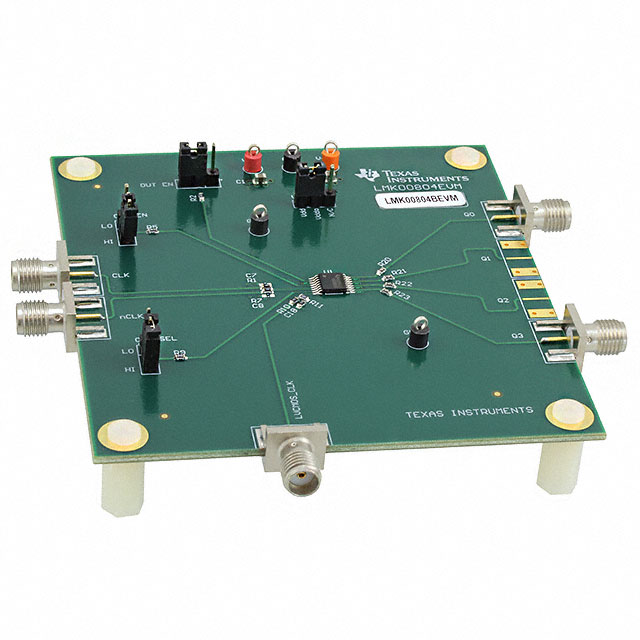

| Specification | LMK00804BEVM |

|---|---|

| Embedded | False |

| Function | Clock Buffer |

| Secondary Attributes | SMA Connectors |

| Supplied Contents | Board(s) |

| Type | Timing |

| Utilized IC / Part | LMK00804B |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 178.80 | |

Description

General part information

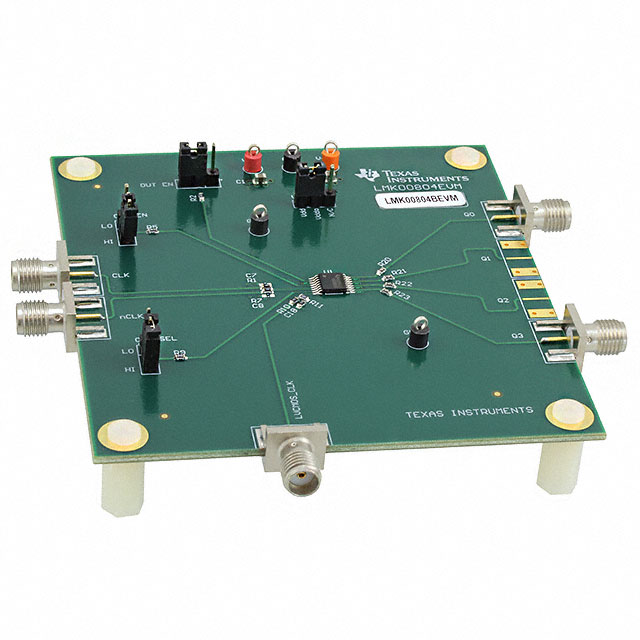

LMK00804B-Q1 Series

The LMK00804B-Q1 is a high-performance clock fan-out buffer and level translator that can distribute up to four LVCMOS/LVTTL outputs (3.3-V, 2.5-V, 1.8-V, or 1.5-V levels) from one of two selectable inputs that can accept differential or single-ended inputs. The clock enable input is synchronized internally to eliminate runt or glitch pulses on the outputs when the clock enable terminal is asserted or deasserted. The outputs are held in logic low state when the clock is disabled. The LMK00804B-Q1 can also distribute a low-jitter clock across four transceivers and can improve the overall target detection and resolution in a cascaded mmWave radar system.

The LMK00804B-Q1 is a high-performance clock fan-out buffer and level translator that can distribute up to four LVCMOS/LVTTL outputs (3.3-V, 2.5-V, 1.8-V, or 1.5-V levels) from one of two selectable inputs that can accept differential or single-ended inputs. The clock enable input is synchronized internally to eliminate runt or glitch pulses on the outputs when the clock enable terminal is asserted or deasserted. The outputs are held in logic low state when the clock is disabled. The LMK00804B-Q1 can also distribute a low-jitter clock across four transceivers and can improve the overall target detection and resolution in a cascaded mmWave radar system.

Documents

Technical documentation and resources