ADC12DJ4000RFAAV

ActiveRF-SAMPLING 12-BIT ADC WITH 4-GSPS DUAL CHANNEL OR 8-GSPS SINGLE CHANNEL

Deep-Dive with AI

Search across all available documentation for this part.

ADC12DJ4000RFAAV

ActiveRF-SAMPLING 12-BIT ADC WITH 4-GSPS DUAL CHANNEL OR 8-GSPS SINGLE CHANNEL

Technical Specifications

Parameters and characteristics for this part

| Specification | ADC12DJ4000RFAAV |

|---|---|

| Architecture | SAR |

| Configuration | ADC |

| Data Interface | JESD204B/C |

| Input Type | Differential |

| Mounting Type | Surface Mount |

| Number of A/D Converters | 2 |

| Number of Bits | 12 bits |

| Number of Inputs | 8 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

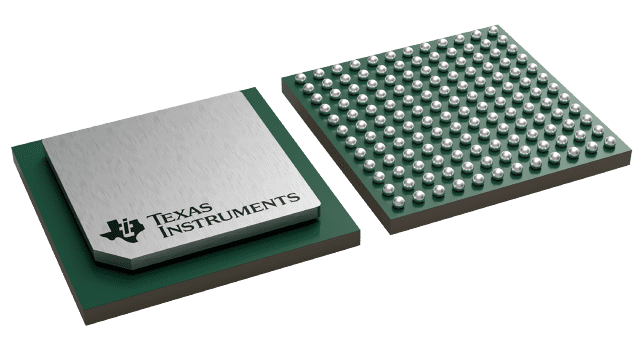

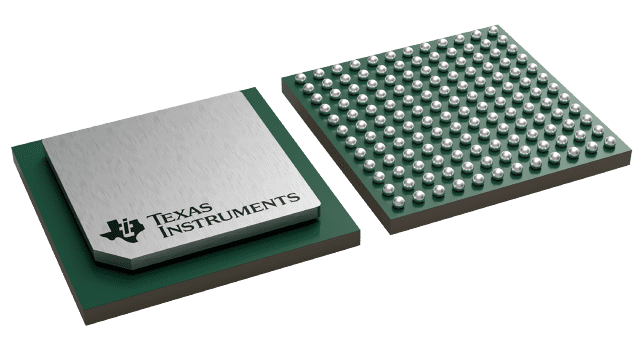

| Package / Case | FCBGA, 144-FBGA |

| Ratio - S/H:ADC | 2:2 |

| Reference Type | External |

| Sampling Rate (Per Second) | 8 G |

| Supplier Device Package | 144-FCBGA (10x10) |

| Voltage - Supply, Analog [Max] | 2 V, 1.15 V |

| Voltage - Supply, Analog [Min] | 1.8 V, 1.05 V |

| Voltage - Supply, Digital [Max] | 1.15 V |

| Voltage - Supply, Digital [Min] | 1.05 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 1 | $ 1970.23 | |

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 1843.20 | |

| 100 | $ 1689.60 | |||

| 250 | $ 1597.44 | |||

| 1000 | $ 1536.00 | |||

Description

General part information

ADC12DJ4000RF Series

The ADC12DJ4000RF device is an RF-sampling, giga-sample, analog-to-digital converter (ADC) that can directly sample input frequencies from DC to above 10 GHz. ADC12DJ4000RF can be configured as a dual-channel, 4 GSPS ADC or single-channel, 8 GSPS ADC. Support of a useable input frequency range of up to 10GHz enables direct RF sampling of L-band, S-band, C-band, and X-band for frequency agile systems.

The ADC12DJ4000RF uses a high-speed JESD204C output interface with up to 16 serialized lanes supporting up to 17.16Gbps line rate. Deterministic latency and multi-device synchronization is supported through JESD204C subclass-1. The JESD204C interface can be configured to trade-off line rate and number of lanes. Both 8b/10b and 64b/66b data encoding schemes are supported. 64b/66b encoding supports forward error correction (FEC) for improved bit error rates. The interface is backwards compatible with JESD204B receivers.

Innovative synchronization features, including noiseless aperture delay adjustment and SYSREF windowing, simplify system design for multi-channel applications. Optional digital down converters (DDCs) are available to provide digital conversion to baseband and to reduce the interface rate. A programmable FIR filter allows on-chip equalization.