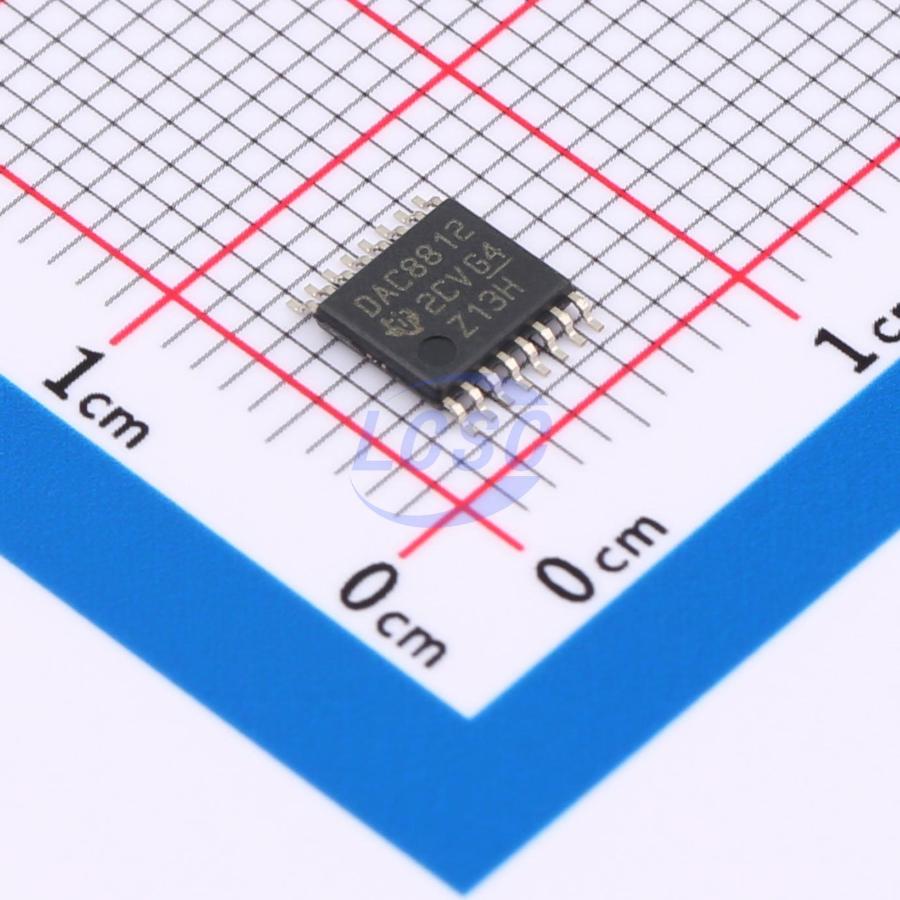

DAC8812ICPWR

Active500NS SPI 1LSB 2.7V~5.5V 16BIT TSSOP-16 DIGITAL TO ANALOG CONVERTERS (DAC) ROHS

Deep-Dive with AI

Search across all available documentation for this part.

DAC8812ICPWR

Active500NS SPI 1LSB 2.7V~5.5V 16BIT TSSOP-16 DIGITAL TO ANALOG CONVERTERS (DAC) ROHS

Technical Specifications

Parameters and characteristics for this part

| Specification | DAC8812ICPWR |

|---|---|

| Architecture | Multiplying DAC |

| Data Interface | SPI |

| Differential Output | False |

| INL/DNL (LSB) | ±1 (Max) |

| Mounting Type | Surface Mount |

| Number of Bits | 16 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output Type | Current - Unbuffered |

| Package / Case | 16-TSSOP |

| Package / Case [x] | 0.173 in |

| Package / Case [y] | 4.4 mm |

| Reference Type | External |

| Settling Time | 500 ns |

| Supplier Device Package | 16-TSSOP |

| Voltage - Supply, Analog [Max] | 5.5 V |

| Voltage - Supply, Analog [Min] | 2.7 V |

| Voltage - Supply, Digital [Max] | 5.5 V |

| Voltage - Supply, Digital [Min] | 2.7 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tape & Reel (TR) | 2000 | $ 16.19 | |

| LCSC | Piece | 1 | $ 21.11 | |

| 10 | $ 20.12 | |||

| 30 | $ 18.42 | |||

| 100 | $ 16.93 | |||

| Texas Instruments | LARGE T&R | 1 | $ 21.12 | |

| 100 | $ 18.45 | |||

| 250 | $ 14.23 | |||

| 1000 | $ 12.72 | |||

Description

General part information

DAC8812 Series

The DAC8812 is a dual, 16-bit, current-output digital-to-analog converter (DAC) designed to operate from a single 2.7-V to 5.5-V supply.

The applied external reference input voltage VREFdetermines the full-scale output current. An internal feedback resistor (RFB) provides temperature tracking for the full-scale output when combined with an external I-to-V precision amplifier.

A double-buffered, serial data interface offers high-speed, 3-wire, SPI and microcontroller compatible inputs using serial data in (SDI), clock (CLK), and a chip-select (CS). A common level-sensitive load DAC strobe (LDAC) input allows simultaneous update of all DAC outputs from previously loaded input registers. Additionally, an internal power-on reset forces the output voltage to zero at system turnon. An MSB pin allows system reset assertion (RS) to force all registers to zero code when MSB = 0, or to midscale code when MSB = 1.

Documents

Technical documentation and resources