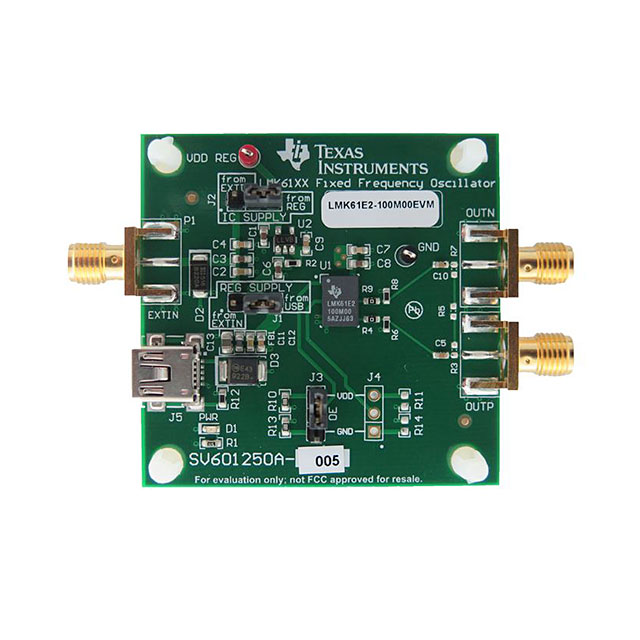

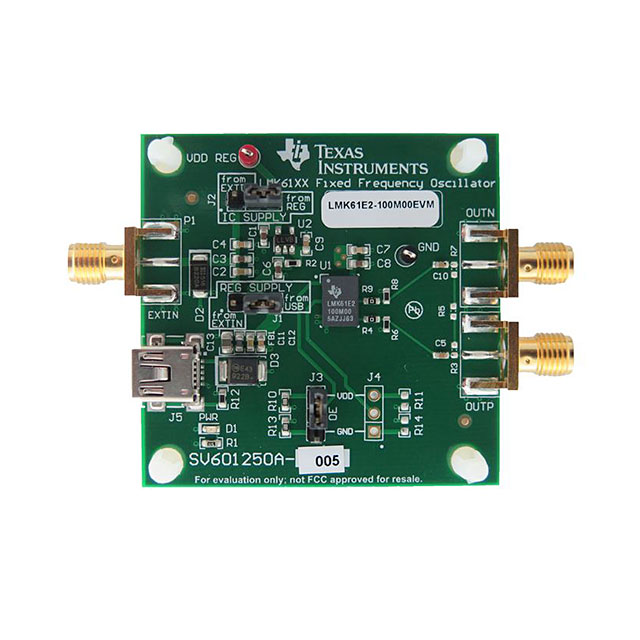

LMK61E2-100M00EVM

ActiveEVAL BOARD FOR LMK61E2-100M00

Deep-Dive with AI

Search across all available documentation for this part.

LMK61E2-100M00EVM

ActiveEVAL BOARD FOR LMK61E2-100M00

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | LMK61E2-100M00EVM |

|---|---|

| Supplied Contents | Board(s) |

| Type | Timing |

| Utilized IC / Part | LMK61E2-100M00 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 1 | $ 94.80 | |

Description

General part information

LMK61E0-050M Series

The LMK61E0 family of ultra-low jitter PLLatinumTMprogrammable oscillators use fractional-N frequency synthesizers with integrated VCOs to generate commonly used reference clocks. The LMK61E0M supports 3.3-V LVCMOS outputs. The device features self start-up from on-chip EEPROM to generate a factory programmed default output frequency, or the device registers and EEPROM settings are fully programmable in-system through I2C serial interface. The device provides fine and coarse frequency margining control through I2C serial interface, making it a digitally-controlled oscillator (DCXO).

The PLL feedback divider can be updated to adjust the output frequency without spikes or glitches in steps of <1ppb using a PFD of 12.5 MHz (R divider=4, doubler disabled) for compatibility with xDSL requirements, or in steps of <5.2 ppb using a PFD of 100 MHz (R divider=1, doubler enabled) for compatibility with broadcast video requirements. The frequency margining features also facilitate system design verification tests (DVT), such as standards compliance and system timing margin testing.

The LMK61E0 family of ultra-low jitter PLLatinumTMprogrammable oscillators use fractional-N frequency synthesizers with integrated VCOs to generate commonly used reference clocks. The LMK61E0M supports 3.3-V LVCMOS outputs. The device features self start-up from on-chip EEPROM to generate a factory programmed default output frequency, or the device registers and EEPROM settings are fully programmable in-system through I2C serial interface. The device provides fine and coarse frequency margining control through I2C serial interface, making it a digitally-controlled oscillator (DCXO).

Documents

Technical documentation and resources