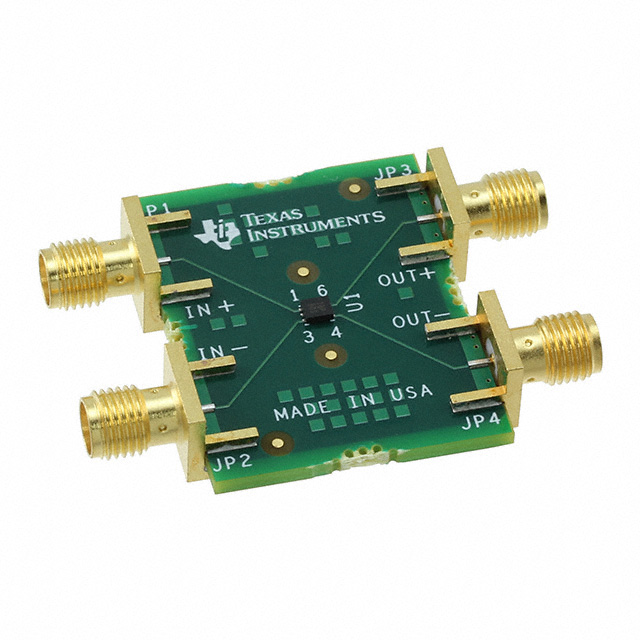

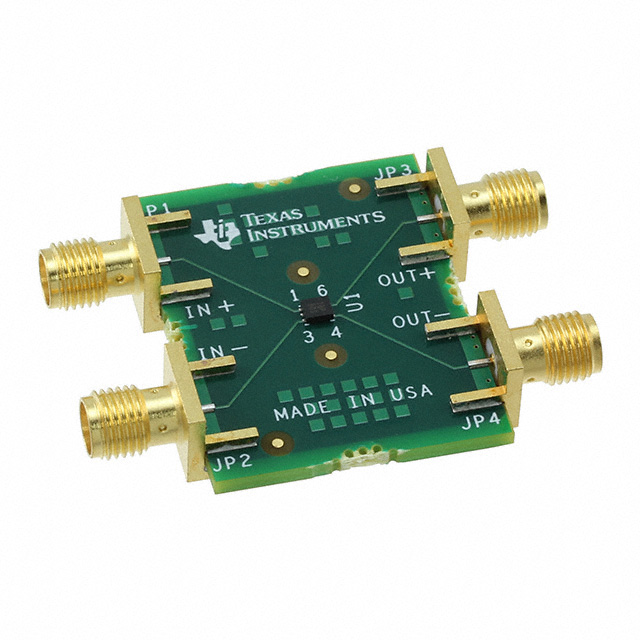

DS80EP100-EVK

ObsoleteEVAL MODULE FOR DS80EP100

Deep-Dive with AI

Search across all available documentation for this part.

DS80EP100-EVK

ObsoleteEVAL MODULE FOR DS80EP100

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | DS80EP100-EVK |

|---|---|

| Function | Cable Equalizer |

| Supplied Contents | Board(s) |

| Type | Interface |

| Utilized IC / Part | DS80EP100 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 118.80 | |

Description

General part information

DS80EP100 Series

TI’s Power-saver equalizer compensates for transmission medium losses and minimizes medium-induced deterministic jitter. Performance is guaranteed over the full range of 5 to 12.5 Gbps. The DS80EP100 requires no power to operate. The equalizer operates anywhere in the data path to minimize media-induced deterministic jitter in both FR4 traces and cable applications. Symmetric I/O structures support full duplex or half duplex applications. Linear compensation is provided independent of line coding or protocol. The device is ideal for both bi-level and multi-level signaling.

The equalizer is available in a 6 pin leadless WSON package with a space saving 2.2 mm X 2.5 mm footprint. This tiny package provides maximum flexibility in placement and routing of the Power-saver equalizer.

TI’s Power-saver equalizer compensates for transmission medium losses and minimizes medium-induced deterministic jitter. Performance is guaranteed over the full range of 5 to 12.5 Gbps. The DS80EP100 requires no power to operate. The equalizer operates anywhere in the data path to minimize media-induced deterministic jitter in both FR4 traces and cable applications. Symmetric I/O structures support full duplex or half duplex applications. Linear compensation is provided independent of line coding or protocol. The device is ideal for both bi-level and multi-level signaling.

Documents

Technical documentation and resources