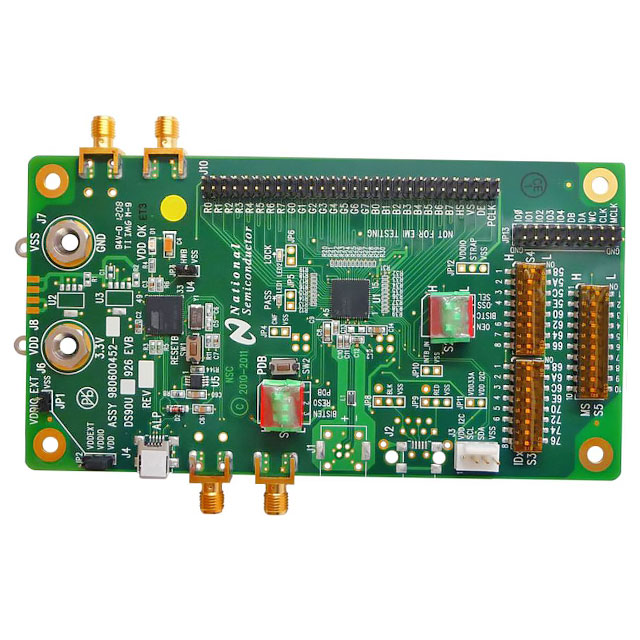

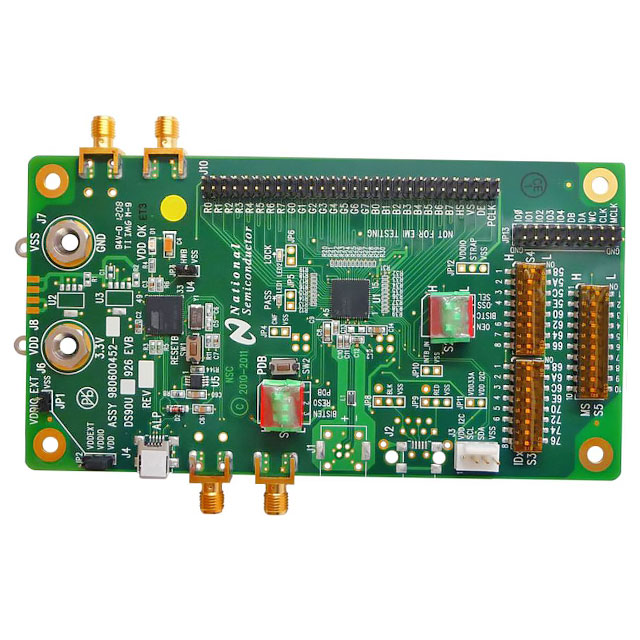

DS90UB926QSEVB/NOPB

ActiveMODULE EVAL FOR DS90UB926QS

Deep-Dive with AI

Search across all available documentation for this part.

DS90UB926QSEVB/NOPB

ActiveMODULE EVAL FOR DS90UB926QS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | DS90UB926QSEVB/NOPB |

|---|---|

| Contents | Cable(s), Board(s) |

| Function | Deserializer |

| Secondary Attributes | I2C Interface(s) |

| Supplied Contents | Cable(s), Board(s) |

| Type | Interface |

| Utilized IC / Part | DS90UB926Q |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 478.80 | |

Description

General part information

DS90UB926Q-Q1 Series

The DS90UB926Q-Q1 deserializer, in conjunction with the DS90UB925Q-Q1 serializer, provides a complete digital interface for concurrent transmission of high-speed video, audio, and control data for automotive display and image-sensing applications.

This chipset translates a parallel RGB video interface into a single-pair high-speed serialized interface. The serial bus scheme, FPD-Link III, supports full duplex of high-speed forward data transmission and low-speed backchannel communication over a single differential link. Consolidation of video data and control over a single differential pair reduces the interconnect size and weight, while also eliminating skew issues and simplifying system design.

The DS90UB926Q-Q1 deserializer recovers the RGB data, three video control signals, and four synchronized I2S audio signals. The device extracts the clock from a high-speed serial stream. An output LOCK pin provides the link status if the incoming data stream is locked, without the use of a training sequence or special SYNC patterns, as well as a reference clock.

Documents

Technical documentation and resources