AD5317R Series

+2.5 V to +5.5 V, 400µA, Quad Rail-To-Rail Output 10-Bit DAC

Manufacturer: Analog Devices

Catalog

+2.5 V to +5.5 V, 400µA, Quad Rail-To-Rail Output 10-Bit DAC

Key Features

• Reset to zero scale or midscale (RSTSEL pin)

• 1.8 V logic compatibility

• 50 MHz SPI with readback or daisy chain

• Low glitch: 0.5 nV-sec

• Low power: 3.3 mW at 3 V

• 2.7 V to 5.5 V power supply

• −40°C to +105°C temperature range

• Low drift 2.5 V reference: 2 ppm/°C typical

• Tiny package: 3 mm × 3 mm, 16-lead LFCSP

• Total unadjusted error (TUE): ±0.1% of FSR maximum

• Offset error: ±1.5 mV maximum

• Gain error: ±0.1% of FSR maximum

• High drive capability: 20 mA, 0.5 V from supply rails

• User selectable gain of 1 or 2 (GAIN pin)

• Precision DC Performance. Total unadjusted error: ±0.1% of FSR maximum

• Offset error: ±1.5 mV maximum Gain error: ±0.1% of FSR maximum

• Low Drift 2.5 V On-Chip Reference. 2 ppm/°C typical temperature coefficient 5 ppm/°C maximum temperature coefficient

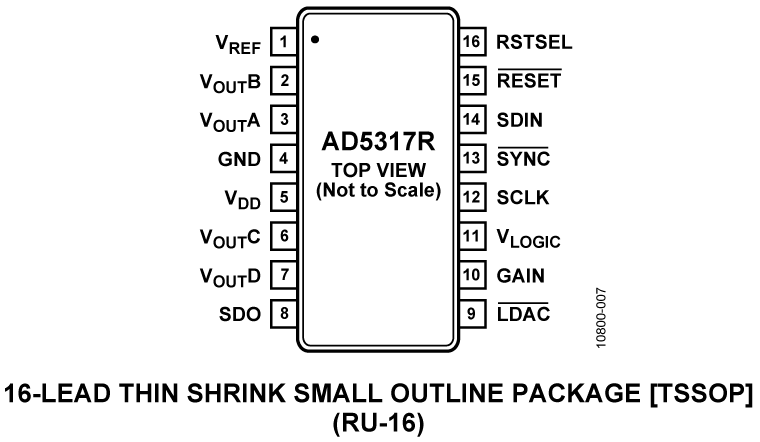

• Two Package Options. 3 mm × 3 mm, 16-lead LFCSP 16-lead TSSOP

• Digital gain and offset adjustment

• Programmable attenuators

• Industrial automation

• Data acquisition systems

Description

AI

The AD5317R, a member of thenanoDAC®family, is a low power, quad, 10-bit buffered voltage output DAC. The device includes a 2.5 V, 2 ppm/°C internal reference (enabled by default) and a gain select pin giving a full-scale output of 2.5 V (gain = 1) or 5 V (gain = 2). The device operates from a single 2.7 V to 5.5 V supply, is guaranteed monotonic by design, and exhibits less than 0.1% FSR gain error and 1.5 mV offset error performance. The device is available in a 3 mm × 3 mm LFCSP and a TSSOP package.The AD5317R also incorporates a power-on reset circuit and a RSTSEL pin that ensures that the DAC outputs power up to zero scale or midscale and remain at that level until a valid write takes place. Each part contains a per-channel power-down feature that reduces the current consumption of the device to 4 µA at 3 V while in power-down mode.The AD5317R employs a versatile SPI interface that operates at clock rates up to 50 MHz and contains a VLOGICpin intended for 1.8 V/3 V/5 V logic.Product HighlightsPrecision DC Performance. Total unadjusted error: ±0.1% of FSR maximum Offset error: ±1.5 mV maximum Gain error: ±0.1% of FSR maximumLow Drift 2.5 V On-Chip Reference. 2 ppm/°C typical temperature coefficient 5 ppm/°C maximum temperature coefficientTwo Package Options. 3 mm × 3 mm, 16-lead LFCSP 16-lead TSSOPApplicationsDigital gain and offset adjustmentProgrammable attenuatorsIndustrial automationData acquisition systems