570BILF

ActiveMULTIPLIER AND ZERO DELAY BUFFER

Deep-Dive with AI

Search across all available documentation for this part.

570BILF

ActiveMULTIPLIER AND ZERO DELAY BUFFER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 570BILF |

|---|---|

| Differential - Input:Output [custom] | False |

| Differential - Input:Output [custom] | False |

| Frequency - Max [Max] | 170 MHz |

| Input | Clock |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 C |

| Output | CMOS |

| Package / Case | 0.154 in |

| Package / Case | 8-SOIC |

| Package / Case | 3.9 mm |

| PLL | True |

| Ratio - Input:Output | 1:2 |

| Supplier Device Package | 8-SOIC |

| Type | Zero Delay Buffer, Fanout Distribution, Spread Spectrum Clock Generator |

| Voltage - Supply [Max] | 3.45 V |

| Voltage - Supply [Min] | 3.15 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | N/A | 38 | $ 3.62 | |

| Tube | 1 | $ 3.83 | ||

| 10 | $ 3.44 | |||

| 97 | $ 2.82 | |||

| 291 | $ 2.67 | |||

| 582 | $ 2.40 | |||

| 1067 | $ 2.02 | |||

| 2522 | $ 1.92 | |||

| 5044 | $ 1.85 | |||

Description

General part information

570 Series

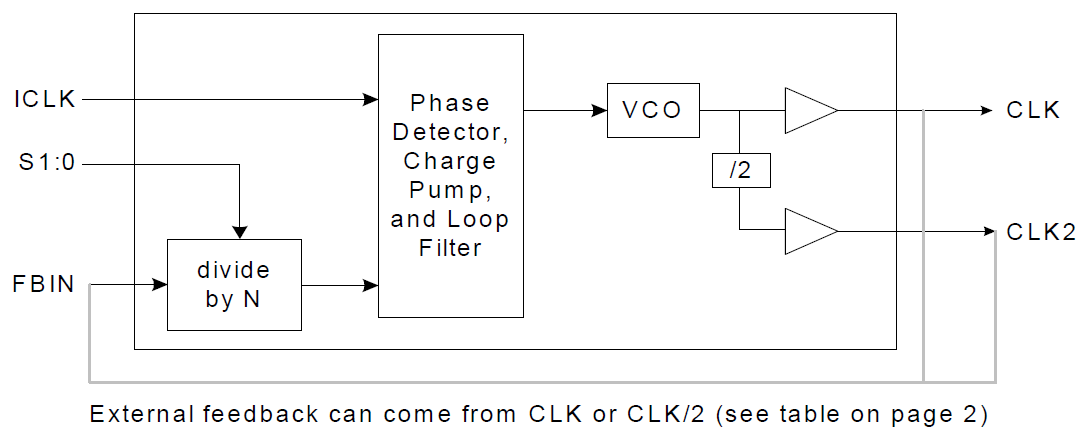

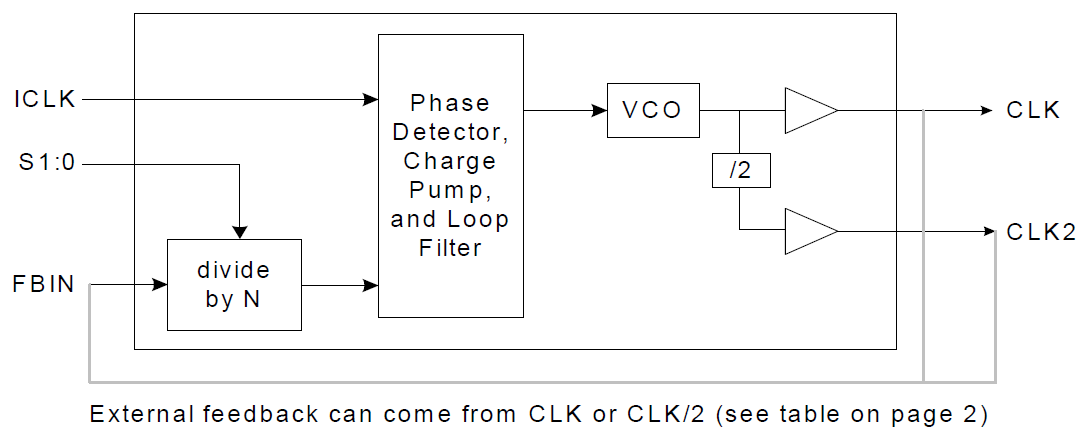

The IDT570 is a high-performance Zero Delay Buffer (ZDB) which integrates IDT's proprietary analog/digital Phase Locked Loop (PLL) techniques. The A version is recommended for 5 V designs and the B version for 3.3 V designs. The chip is part of IDT's ClockBlocks™ family, and was designed as a performance upgrade to meet today's higher speed and lower voltage requirements. The zero delay feature means that the rising edge of the input clock aligns with the rising edges of both output clocks, giving the appearance of no delay through the device. There are two outputs on the chip, one being a low-skew divide by two of the other output. The device incorporates an all-chip power down/tri-state mode that stops the internal PLL and puts both outputs into a high impedance state. The IDT570 is ideal for synchronizing outputs in a large variety of systems, from personal computers to data communications to graphIDT/video. By allowing off-chip feedback paths, the device can eliminate the delay through other devices.

Documents

Technical documentation and resources