Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | TVP7002PZP |

|---|---|

| Applications | Consumer Video |

| Control Interface | I2C |

| Function | Digitizer |

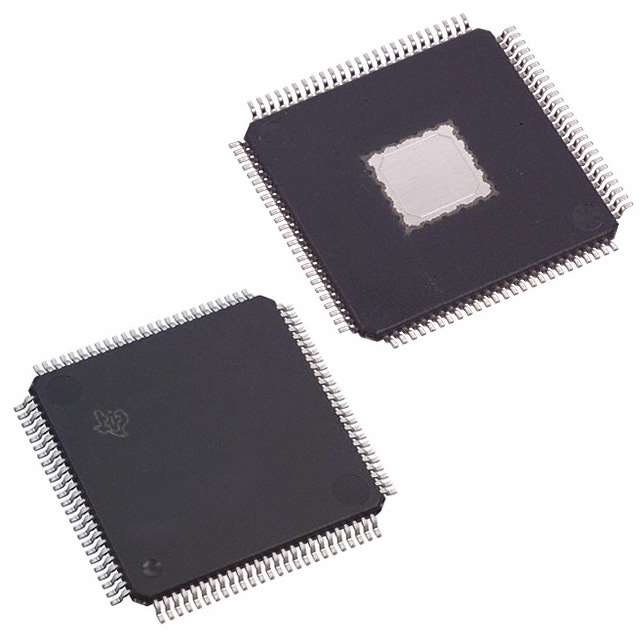

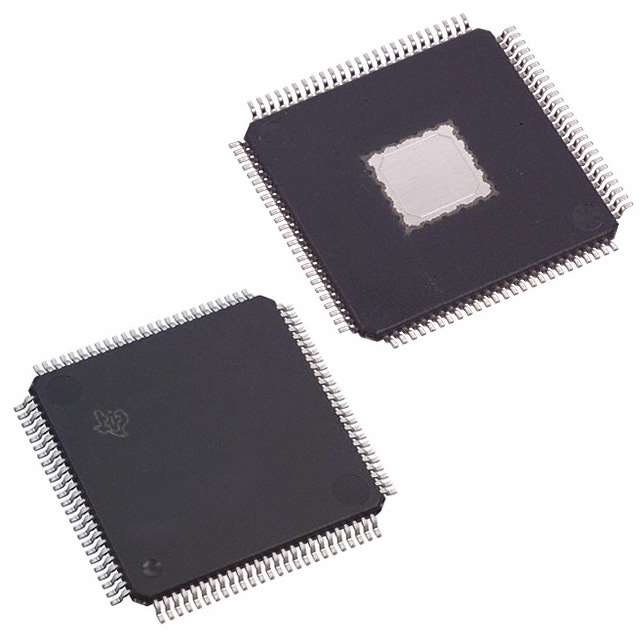

| Mounting Type | Surface Mount |

| Package / Case | 100-TQFP Exposed Pad |

| Supplier Device Package | 100-HTQFP (14x14) |

| Voltage - Supply [Max] | 3.6 V, 2 V |

| Voltage - Supply [Min] | 1.8 V, 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | N/A | 421 | $ 10.72 | |

| Tray | 1 | $ 9.95 | ||

| 10 | $ 8.99 | |||

| 25 | $ 8.57 | |||

| 90 | $ 7.44 | |||

| 270 | $ 7.11 | |||

| 450 | $ 6.48 | |||

| 990 | $ 5.64 | |||

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 7.62 | |

| 100 | $ 6.21 | |||

| 250 | $ 4.88 | |||

| 1000 | $ 4.14 | |||

Description

General part information

TVP7002 Series

The TVP7002 is a complete solution for digitizing video and graphic signals in RGB or YPbPr color spaces. The device supports pixel rates up to 165 MHz. Therefore, it can be used for PC graphics digitizing up to the VESA standard of UXGA (1600 × 1200) resolution at a 60-Hz screen refresh rate, and in video environments for the digitizing of digital TV formats, including HDTV up to 1080p.

The TVP7002 is powered from 3.3-V and 1.9-V supply and integrates a triple high-performance analog-to-digital (A/D) converter with clamping functions and variable gain, independently programmable for each channel. The clamp timing window is provided by an external pulse or can be generated internally. The TVP7002 includes analog slicing circuitry on the SOG inputs to support sync-on-luminance or sync-on-green extraction. In addition, TVP7002 can extract discrete HSYNC and VSYNC from composite sync using a sync slicer.

The TVP7002 also contains a complete horizontal phase-locked loop (PLL) block to generate a pixel clock from the HSYNC input. Pixel clock output frequencies range from 12 MHz to 165 MHz.

Documents

Technical documentation and resources