Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

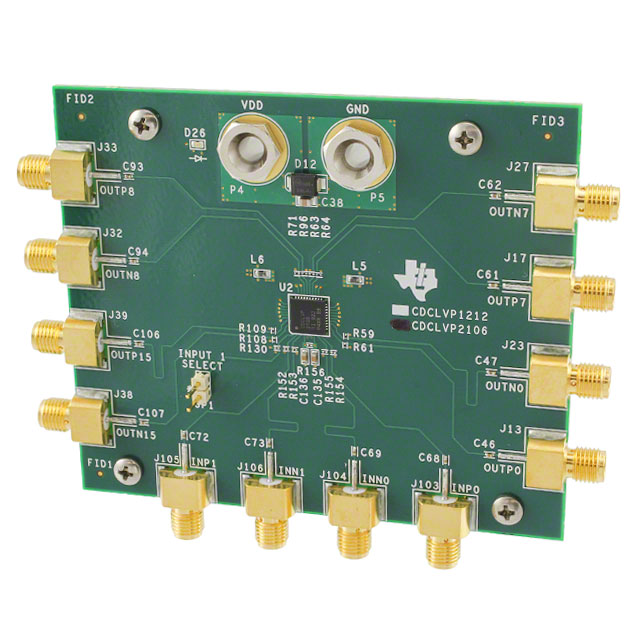

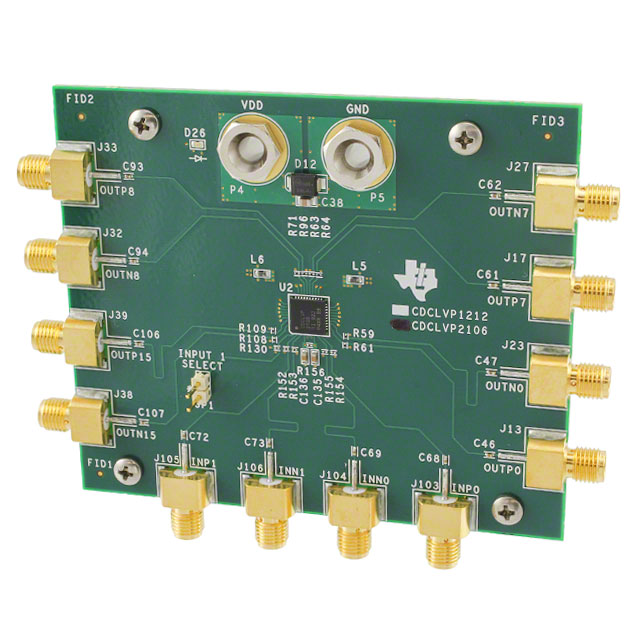

| Specification | CDCLVP2106EVM |

|---|---|

| Embedded | False |

| Function | Clock Buffer |

| Supplied Contents | Board(s) |

| Type | Timing |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 178.80 | |

Description

General part information

CDCLVP2106 Series

The CDCLVP2106 is a highly versatile, low additive jitter buffer that can generate 12 copies of LVPECL clock outputs from two LVPECL, LVDS, or LVCMOS inputs for a variety of communication applications. It has a maximum clock frequency up to 2 GHz. Each buffer block consists of one input that feeds two LVPECL outputs. The overall additive jitter performance is less than 0.1 ps, RMS from 10 kHz to 20 MHz, and overall output skew is as low as 20 ps, making the device a perfect choice for use in demanding applications.

The CDCLVP2106 clock buffer distributes two clock inputs (IN0, IN1) to 12 pairs of differential LVPECL clock outputs (OUT0, OUT11) with minimum skew for clock distribution. Each buffer block consists of one input that feeds two LVPECL clock outputs. The inputs can be LVPECL, LVDS, or LVCMOS/LVTTL.

The CDCLVP2106 is specifically designed for driving 50-Ω transmission lines. When driving the inputs in single-ended mode, the LVPECL bias voltage (VAC_REF) should be applied to the unused negative input pin. However, for high-speed performance up to 2 GHz, differential mode is strongly recommended.

Documents

Technical documentation and resources