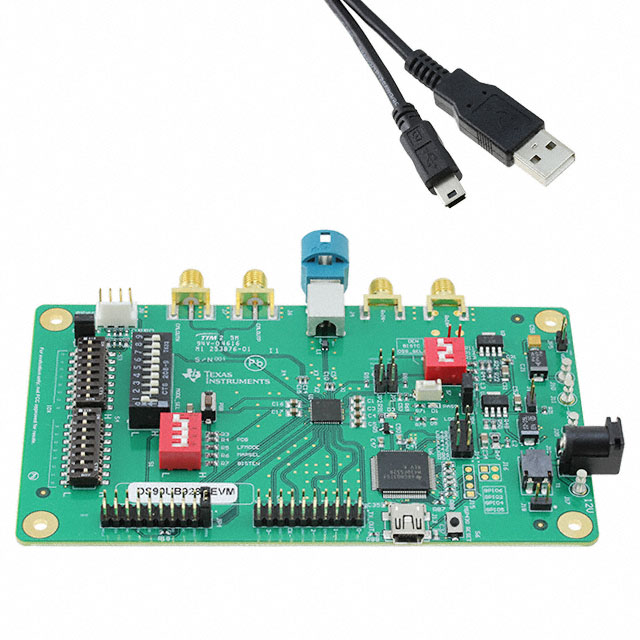

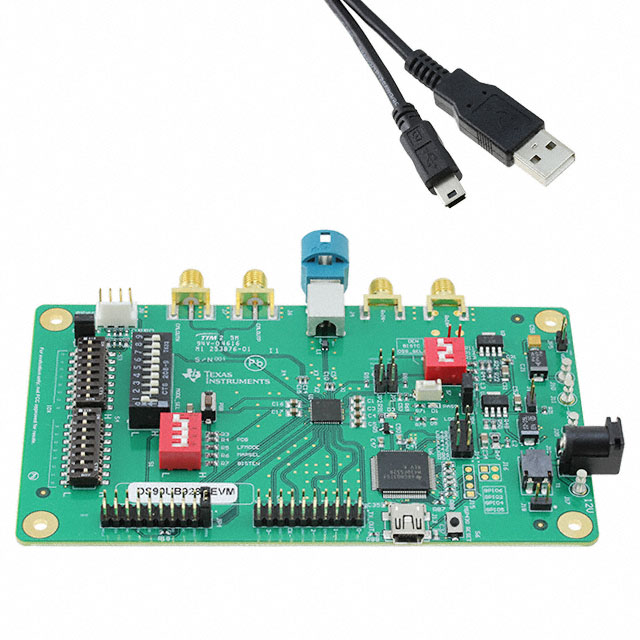

DS90UB928QEVM

ActiveFPD-LINK III DESERIALIZER EVALUATION MODULE

Deep-Dive with AI

Search across all available documentation for this part.

DS90UB928QEVM

ActiveFPD-LINK III DESERIALIZER EVALUATION MODULE

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | DS90UB928QEVM |

|---|---|

| Function | Deserializer |

| Supplied Contents | Board(s) |

| Type | Interface |

| Utilized IC / Part | DS90UB928Q |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 358.80 | |

Description

General part information

DS90UB928Q-Q1 Series

The DS90UB928Q-Q1 deserializer, in conjunction with a DS90UB925Q-Q1 or DS90UB927Q-Q1 serializer, provides a solution for distribution of digital video and audio within automotive infotainment systems. The device converts a high-speed serialized interface with an embedded clock, delivered over a single signal pair (FPD-Link III), to four LVDS data/control streams, one LVDS clock pair (OpenLDI (FPD-Link)), and I2S audio data. The serial bus scheme, FPD-Link III, supports high-speed forward channel data transmission and low-speed full duplex back channel communication over a single differential link. Consolidation of audio, video data and control over a single differential pair reduces the interconnect size and weight, while also eliminating skew issues and simplifying system design.

Adaptive input equalization of the serial input stream provides compensation for transmission medium losses and deterministic jitter. EMI is minimized by the use of low voltage differential signaling.

The DS90UB928Q-Q1 deserializer, in conjunction with a DS90UB925Q-Q1 or DS90UB927Q-Q1 serializer, provides a solution for distribution of digital video and audio within automotive infotainment systems. The device converts a high-speed serialized interface with an embedded clock, delivered over a single signal pair (FPD-Link III), to four LVDS data/control streams, one LVDS clock pair (OpenLDI (FPD-Link)), and I2S audio data. The serial bus scheme, FPD-Link III, supports high-speed forward channel data transmission and low-speed full duplex back channel communication over a single differential link. Consolidation of audio, video data and control over a single differential pair reduces the interconnect size and weight, while also eliminating skew issues and simplifying system design.

Documents

Technical documentation and resources