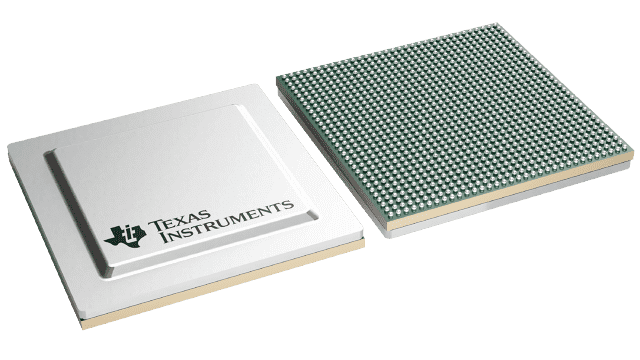

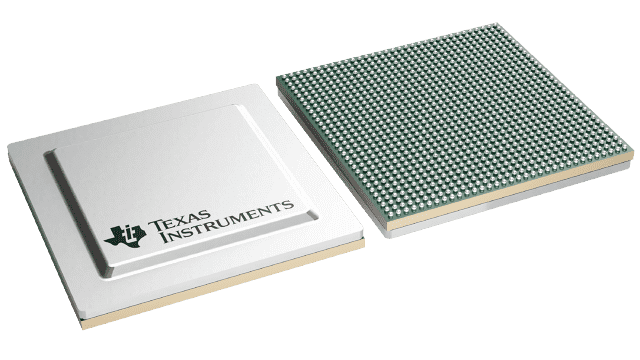

AM5K2E04XABD4

ActiveSOC AM5K2EX ARM CORTEX A15 28NM 1089-PIN FCBGA TRAY

Deep-Dive with AI

Search across all available documentation for this part.

AM5K2E04XABD4

ActiveSOC AM5K2EX ARM CORTEX A15 28NM 1089-PIN FCBGA TRAY

Technical Specifications

Parameters and characteristics for this part

| Specification | AM5K2E04XABD4 |

|---|---|

| Additional Interfaces | SPI, UART, EBI/EMI, PCIe, TSIP, I2C, USIM |

| Co-Processors/DSP | Network |

| Core Processor | ARM® Cortex®-A15 |

| Ethernet | 1GbE (8), 10GbE (2) |

| Graphics Acceleration | False |

| Mounting Type | Surface Mount |

| Number of Cores/Bus Width [custom] | 4 Core |

| Number of Cores/Bus Width [custom] | 32 Bit |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | 0 °C |

| Package / Case | 1089-BFBGA, FCBGA |

| RAM Controllers | DDR3, SRAM |

| Speed | 1.4 GHz |

| Supplier Device Package | 1089-FCBGA (27x27) |

| USB | USB 3.0 (2) |

| Voltage - I/O | 1.5 V, 1.35 V, 3.3 V, 1.8 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 40 | $ 148.94 | |

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 147.47 | |

| 100 | $ 143.03 | |||

| 250 | $ 119.08 | |||

| 1000 | $ 110.88 | |||

Description

General part information

AM5K2E04 Series

The AM5K2E0x is a high performance device based on TI’s KeyStone II Multicore SoC Architecture, incorporating the most performance-optimized Cortex-A15 processor dual-core or quad-core CorePac that can run at a core speed of up to 1.4 GHz. TI’s AM5K2E0x device enables a high performance, power-efficient and easy to use platform for developers of a broad range of applications such as enterprise grade networking end equipment, data center networking, avionics and defense, medical imaging, test and automation.

TI’s KeyStone II Architecture provides a programmable platform integrating various subsystems (for example, ARM CorePac (Cortex-A15 Processor Quad Core CorePac), network processing, and uses a queue-based communication system that allows the device resources to operate efficiently and seamlessly. This unique device architecture also includes a TeraNet switch that enables the wide mix of system elements, from programmable cores to high-speed IO, to each operate at maximum efficiency with no blocking or stalling.

The AM5K2E0x KeyStone II device integrates a large amount of on-chip memory. The Cortex-A15 processor cores each have 32KB of L1Data and 32KB of L1 Instruction cache. The up to four Cortex A15 cores in the ARM CorePac share a 4MB L2 Cache. The device also integrates 2MB of Multicore Shared Memory (MSMC) that can be used as a shared L3 SRAM. All L2 and MSMC memories incorporate error detection and error correction. For fast access to external memory, this device includes a 64-bit DDR-3 (72-bit with ECC support) external memory interface (EMIF) running at 1600 MTPS.

Documents

Technical documentation and resources