ISL6548ACRZA

ObsoleteACPI REGULATOR/CONTROLLER FOR DUAL CHANNEL DDR MEMORY SYSTEMS

Deep-Dive with AI

Search across all available documentation for this part.

ISL6548ACRZA

ObsoleteACPI REGULATOR/CONTROLLER FOR DUAL CHANNEL DDR MEMORY SYSTEMS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | ISL6548ACRZA |

|---|---|

| Applications | Memory, DDR/DDR2 Regulator |

| Current - Supply | 7 mA |

| Mounting Type | Surface Mount |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Package / Case | 28-VQFN Exposed Pad |

| Supplier Device Package | 28-QFN (6x6) |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 70 | $ 4.35 | |

| Tube | 1 | $ 7.24 | ||

| 10 | $ 6.54 | |||

| 50 | $ 6.23 | |||

| 100 | $ 5.41 | |||

| 250 | $ 5.17 | |||

Description

General part information

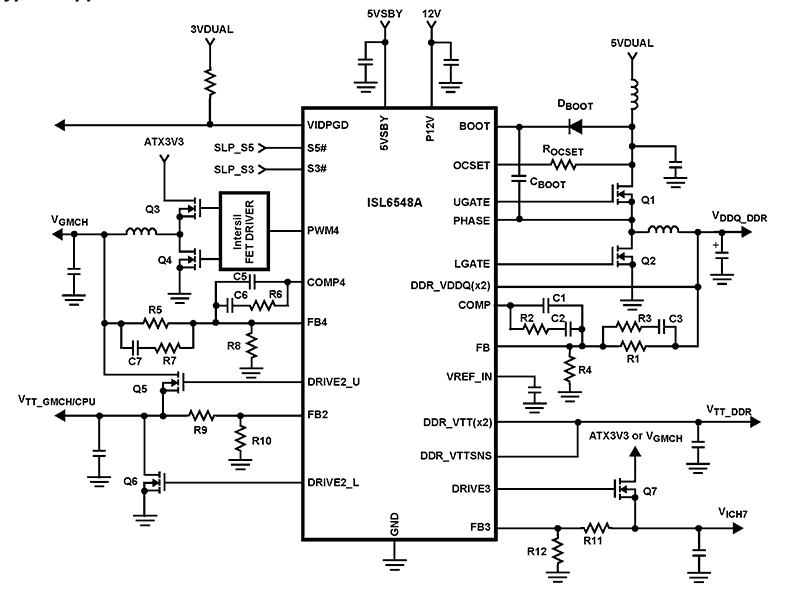

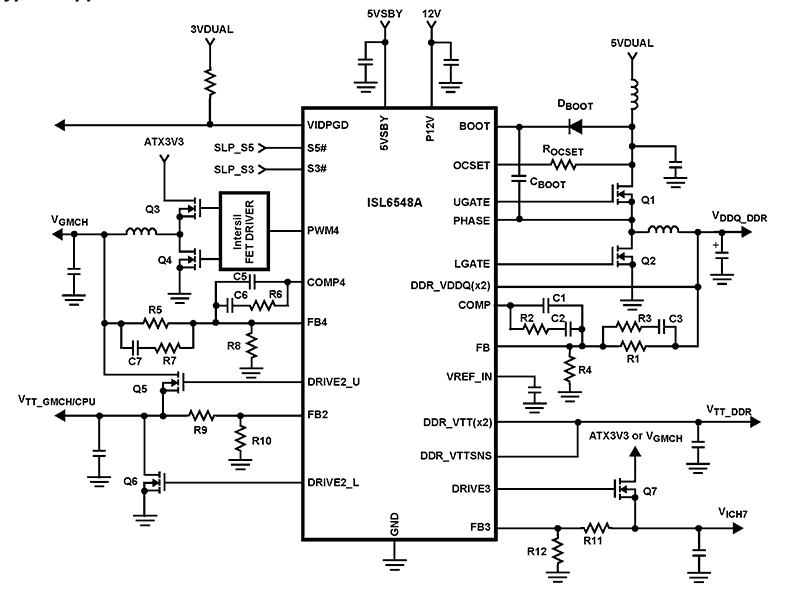

ISL6548A Series

The ISL6548A provides a complete ACPI compliant power solution for up to 4 DIMM dual channel DDR/DDR2 Memory systems. Included are both a synchronous buck controller to supply VDDQduring S0/S1 and S3 states. During S0/S1 state, a fully integrated sink-source regulator generates an accurate (VDDQ/2) high current VTTvoltage without the need for a negative supply. A second PWM controller, which requires external MOSFET drivers, is available for regulation of the GMCH Core voltage. A sink/source LDO controller is also integrated for the CPU/GMCH VTTtermination voltage regulation. Another LDO is available for the ICH7 voltage. The switching PWM controller drives two N-Channel MOSFETs in a synchronous-rectified buck converter topology. The synchronous buck converter uses voltage-mode control with fast transient response. The switching regulator provides a maximum static regulation tolerance of ±2% over line, load, and temperature ranges. The output is user-adjustable by means of external resistors down to 0. 8V. An integrated soft-start feature brings all outputs into regulation in a controlled manner when returning to S0/S1 state from any sleep state. During S0 the VIDPGD signal indicates that the GMCH and CPU VTTtermination voltage is within spec and operational. All outputs, except VICH7, have undervoltage protection. The switching regulator also has overvoltage and overcurrent protection. Thermal shutdown is integrated.

Documents

Technical documentation and resources