Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

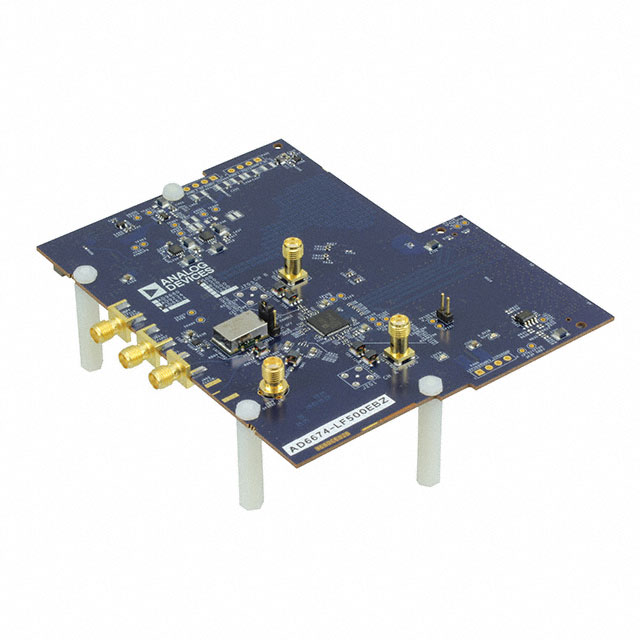

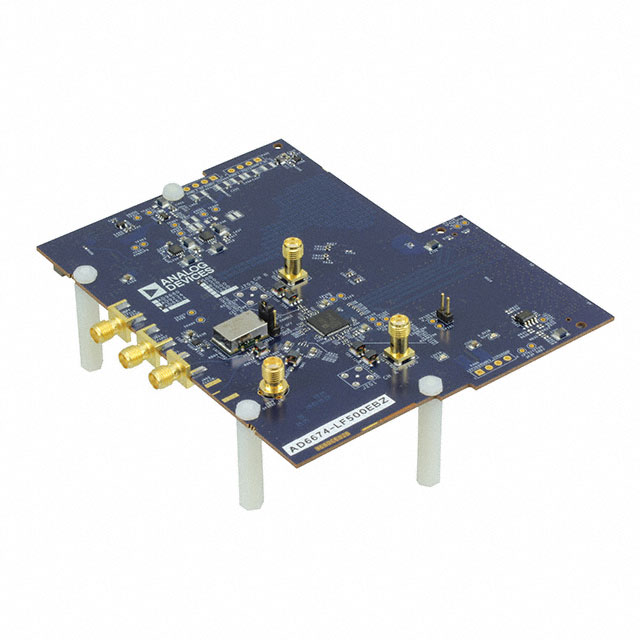

| Specification | AD6674-LF500EBZ |

|---|---|

| Contents | Board(s) |

| Type | Receiver |

| Utilized IC / Part | AD6674 |

AD6674 Series

385 MHz BW IF Diversity Receiver

| Part | Supplied Contents | For Use With/Related Products | Type | Utilized IC / Part | Contents | Package / Case | Mounting Type | Frequency | Supplier Device Package | Function |

|---|---|---|---|---|---|---|---|---|---|---|

Analog Devices | Board(s) | AD6674 | Receiver | |||||||

Analog Devices | Board(s) | AD6674 | Receiver | |||||||

Analog Devices | Receiver | AD6674 | Board(s) | |||||||

Analog Devices | 64-WFQFN Exposed Pad CSP | Surface Mount | 385 MHz | 64-LFCSP (9x9) | IF Receiver | |||||

Analog Devices | 64-WFQFN Exposed Pad CSP | Surface Mount | 385 MHz | 64-LFCSP (9x9) | IF Receiver | |||||

Analog Devices | 64-WFQFN Exposed Pad CSP | Surface Mount | 385 MHz | 64-LFCSP (9x9) | IF Receiver | |||||

Analog Devices | 64-WFQFN Exposed Pad CSP | Surface Mount | 385 MHz | 64-LFCSP (9x9) | IF Receiver | |||||

Analog Devices | 64-WFQFN Exposed Pad CSP | Surface Mount | 385 MHz | 64-LFCSP (9x9) | IF Receiver |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 730.92 | |

Description

General part information

AD6674 Series

The AD6674 is a 385 MHz bandwidth mixed-signal intermediate frequency (IF) receiver. It consists of two, 14-bit 1.0 GSPS/750 MSPS/500 MSPS analog-to-digital converters (ADC) and various digital signal processing blocks consisting of four wideband DDCs, an NSR, and VDR monitoring. It has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of sampling wide bandwidth analog signals of up to 2 GHz. The AD6674 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.ApplicationsDiversity multiband, multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE, LTE-ADOCSIS 3.0 CMTS upstream receive pathsHFC digital reverse path receivers

Documents

Technical documentation and resources