83940DYLF

ObsoleteLOW SKEW,1-TO-18 LVPECL-TO-LVCMOS/LVTTL FANOUT BUFFER

Deep-Dive with AI

Search across all available documentation for this part.

83940DYLF

ObsoleteLOW SKEW,1-TO-18 LVPECL-TO-LVCMOS/LVTTL FANOUT BUFFER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 83940DYLF |

|---|---|

| Differential - Input:Output | Yes/No |

| Frequency - Max [Max] | 250 MHz |

| Input | SSTL, CML, LVTTL, LVPECL, LVCMOS |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Output | LVCMOS, LVTTL |

| Package / Case | 32-LQFP |

| Ratio - Input:Output [custom] | 18 |

| Ratio - Input:Output [custom] | 2 |

| Supplier Device Package | 32-TQFP (7x7) |

| Type | Fanout Buffer (Distribution) |

| Voltage - Supply [Max] | 2.625 V, 3.465 V |

| Voltage - Supply [Min] | 2.375 V, 3.135 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 40 | $ 13.36 | |

Description

General part information

83940I-01 Series

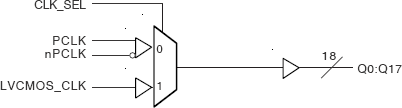

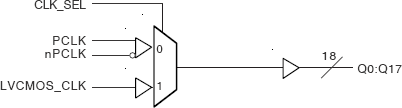

The 83940DI is a low skew, 1-to-18 LVPECL- to-LVCMOS/LVTTL Fanout Buffer. The 83940DI has two selectable clock inputs. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The 83940DI is characterized at full 3.3V and 2.5V or mixed 3.3V core, 2.5V output operating supply modes. Guaranteed output and part-to-part skew characteristics make the 83940DI ideal for those clock distribution applications demanding well defined performance and repeatability.

Documents

Technical documentation and resources