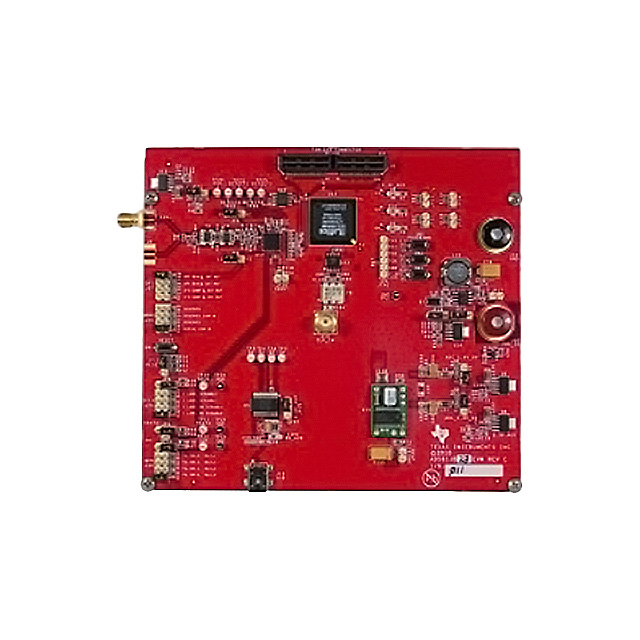

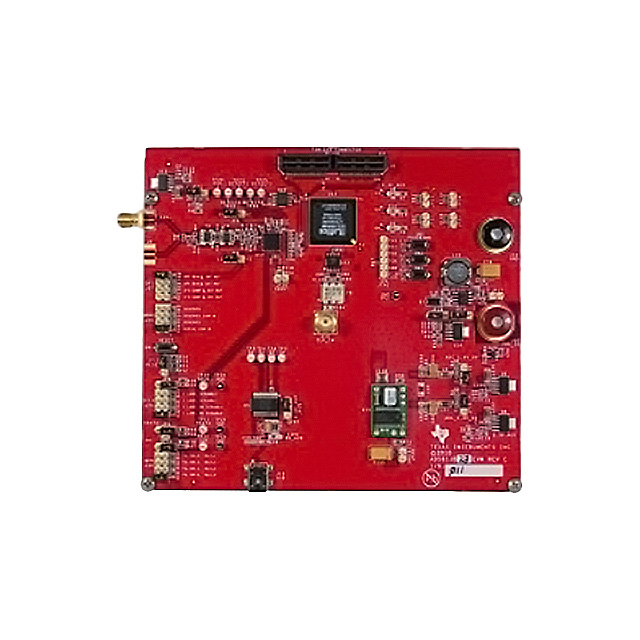

ADS61JB46EVM

ObsoleteEVALUATION MODULE FOR ADS61JB46

Deep-Dive with AI

Search across all available documentation for this part.

ADS61JB46EVM

ObsoleteEVALUATION MODULE FOR ADS61JB46

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | ADS61JB46EVM |

|---|---|

| Data Interface | JESD204A |

| Input Range | 2 Vpp |

| Number of A/D Converters | 1 |

| Number of Bits | 14 |

| Power (Typ) @ Conditions | 583 mW |

| Sampling Rate (Per Second) | 160M |

| Supplied Contents | Board(s) |

| Utilized IC / Part | ADS61JB46 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

ADS61JB46 Series

The ADS61JB46 is a high-performance, low-power, single-channel, analog-to-digital converter with an integrated JESD204A output interface. Available in a 6-mm × 6-mm QFN package, with both single-lane and dual-lane output modes, the device offers an unprecedented level of compactness. The output interface is compatible to the JESD204A standard, with an additional mode (as per the IEEE standard 802.3-2002 part 3, clause 36.2.4.12) to interface seamlessly to the TI TLK family of SERDES transceivers. Equally impressive is the inclusion of an on-chip analog input buffer, providing isolation between the sample-and-hold switches and higher and more consistent input impedance.

The device is specified over the industrial temperature range (–40°C to +85°C).

The ADS61JB46 is a high-performance, low-power, single-channel, analog-to-digital converter with an integrated JESD204A output interface. Available in a 6-mm × 6-mm QFN package, with both single-lane and dual-lane output modes, the device offers an unprecedented level of compactness. The output interface is compatible to the JESD204A standard, with an additional mode (as per the IEEE standard 802.3-2002 part 3, clause 36.2.4.12) to interface seamlessly to the TI TLK family of SERDES transceivers. Equally impressive is the inclusion of an on-chip analog input buffer, providing isolation between the sample-and-hold switches and higher and more consistent input impedance.

Documents

Technical documentation and resources