DS1746WP-120IND+

ActiveY2K-COMPLIANT, NONVOLATILE TIMEKEEPING RAMS

Deep-Dive with AI

Search across all available documentation for this part.

DS1746WP-120IND+

ActiveY2K-COMPLIANT, NONVOLATILE TIMEKEEPING RAMS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | DS1746WP-120IND+ |

|---|---|

| Current - Timekeeping (Max) [Max] | 2 mA |

| Date Format | YY-MM-DD-dd |

| Features | Y2K, Leap Year, NVSRAM |

| Interface | Parallel |

| Memory Size | 1 Mbit |

| Mounting Type | Surface Mount |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 C |

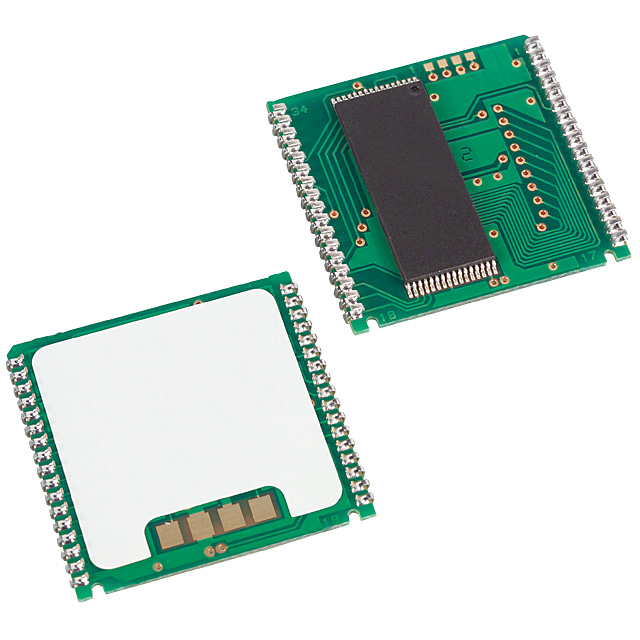

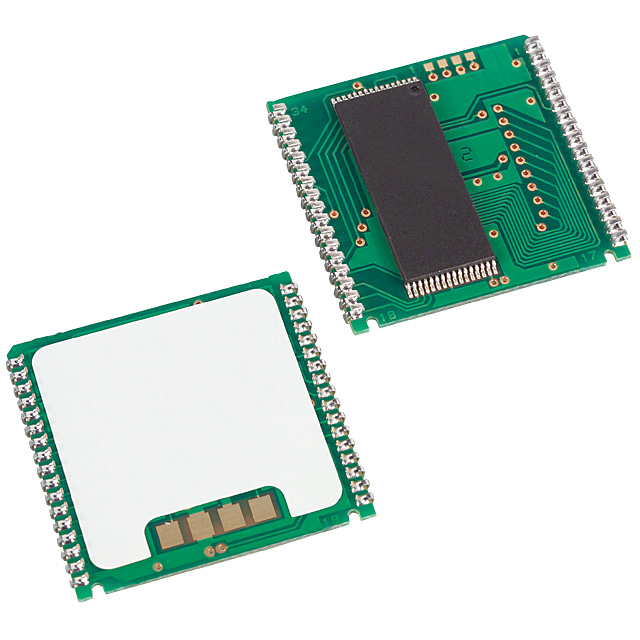

| Package / Case | 34-PowerCap™ Module |

| Supplier Device Package | 34-PowerCap Module |

| Time Format | HH:MM:SS (24 hr) |

| Type | Clock/Calendar |

| Voltage - Supply [Max] | 3.63 V |

| Voltage - Supply [Min] | 2.97 V |

| Voltage - Supply, Battery | 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | Updated |

|---|---|---|---|---|

| Digikey | Tray | 1 | $ 69.21 | <4d |

| 10 | $ 57.36 | |||

| 40 | $ 53.15 | |||

| 120 | $ 50.80 | |||

Description

General part information

DS1746 Series

The DS1746 is a full-function, year-2000-compliant (Y2KC), real-time clock/calendar (RTC) and 128k x 8 nonvolatile static RAM. User access to all registers within the DS1746 is accomplished with a byte-wide interface as shown in Figure 1. The RTC information and control bits reside in the eight uppermost RAM locations. The RTC registers contain century, year, month, date, day, hours, minutes, and seconds data in 24-hour binary-coded decimal (BCD) format. Corrections for the date of each month and leap year are made automatically. The RTC clock registers are double buffered to avoid access of incorrect data that can occur during clock update cycles. The double-buffered system also prevents time loss as the timekeeping countdown continues unabated by access to time register data. The DS1746 also contains its own power-fail circuitry, which deselects the device when the VCCsupply is in an out of tolerance condition. This feature prevents loss of data from unpredictable system operation brought on by low VCCas errant access and update cycles are avoided.