Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

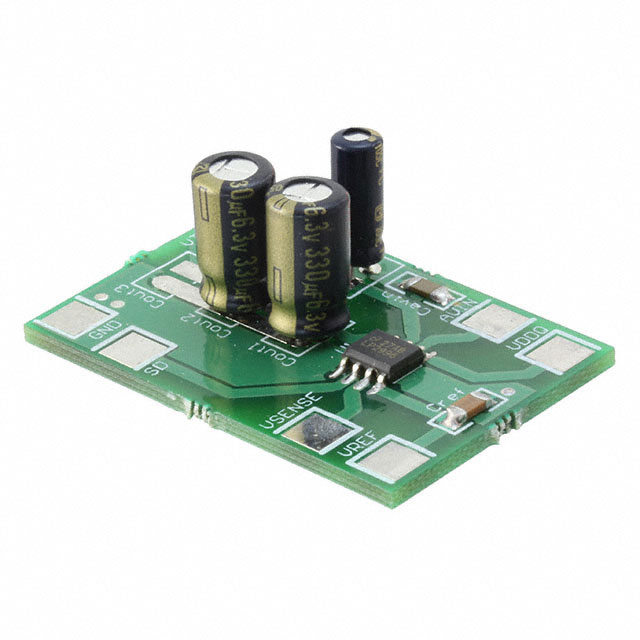

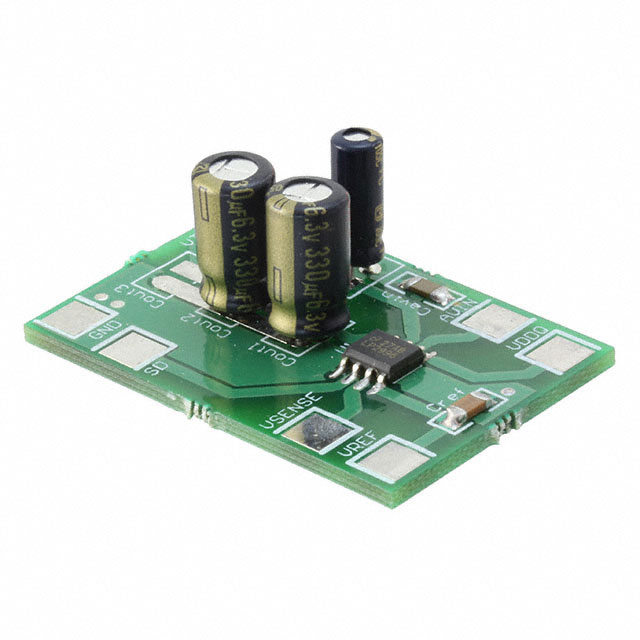

| Specification | LP2996MREVAL |

|---|---|

| Board Type | Fully Populated |

| Channels per IC | 1 - Single |

| Current - Output | 1.5 A |

| Regulator Type | Positive Fixed |

| Supplied Contents | Board(s) |

| Utilized IC / Part | LP2996 |

| Voltage - Input [Max] | 5.5 V |

| Voltage - Input [Min] | 2.2 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

LP2996-N Series

The LP2996-N and LP2996A linear regulators are designed to meet the JEDEC SSTL-2 specifications for termination of DDR-SDRAM. The device also supports DDR2, while LP2996A supports DDR3 and DDR3L VTT bus termination with VDDQminimum of 1.35 V. The device contains a high-speed operational amplifier to provide excellent response to load transients. The output stage prevents shoot through while delivering 1.5-A continuous current and transient peaks up to 3 A in the application as required for DDR-SDRAM termination. The LP2996-N and LP2996A also incorporate a VSENSE pin to provide superior load regulation and a VREF output as a reference for the chipset and DIMMs.

An additional feature found on the LP2996-N and LP2996A is an active-low shutdown (SD) pin that provides Suspend To RAM (STR) functionality. WhenSDis pulled low the VTT output will tri-state providing a high impedance output, but VREF remains active. A power savings advantage can be obtained in this mode through lower quiescent current.

TI recommends the LP2998 and LP2998-Q1 devices for automotive applications and DDR applications that require operating at temperatures below zero.

Documents

Technical documentation and resources