AM6852ATGGHAALZR

ActiveGENERAL PURPOSE SOC WITH DUAL CORE 64-BIT ARM CORTEX-A72, GRAPHICS, 1-PORT PCIE GEN3, USB3.0

Deep-Dive with AI

Search across all available documentation for this part.

AM6852ATGGHAALZR

ActiveGENERAL PURPOSE SOC WITH DUAL CORE 64-BIT ARM CORTEX-A72, GRAPHICS, 1-PORT PCIE GEN3, USB3.0

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | AM6852ATGGHAALZR |

|---|---|

| Additional Interfaces | GPIO, I2C, SPI, QSPI, CANbus, UART/USART, PCIe, DMA, MMC/SD |

| Co-Processors/DSP | ARM® Cortex®-R5F, Multimedia, GPU |

| Core Processor | ARM® Cortex®-A72 |

| Display & Interface Controllers | eDP, MIPI-DSI, DPI |

| Ethernet | 10 Mbps, 1000 Mbps, 100 Mbps |

| Ethernet | 2 |

| Graphics Acceleration | True |

| Mounting Type | Surface Mount |

| Number of Cores/Bus Width | 64 Bit, 2 Core |

| Operating Temperature [custom] | -40 °C, 105 °C |

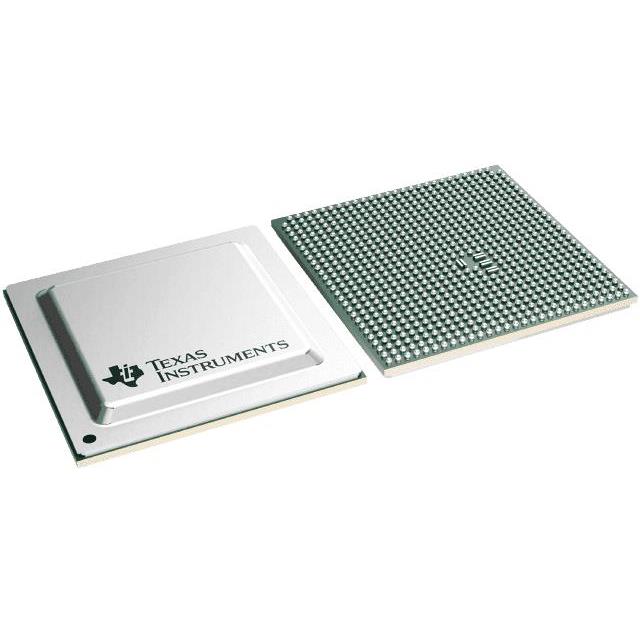

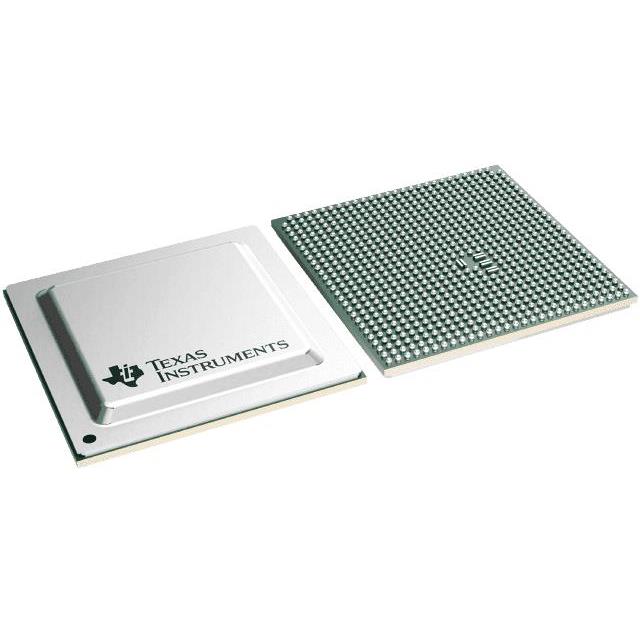

| Package / Case | 770-BFBGA, FCBGA |

| RAM Controllers | LPDDR4 |

| Security Features | MD5, SHA, SMS, AES, ECC, 3DES, DRBG, Random Number Generator, Cryptography, RSA, Secure Boot, PKA |

| Speed | 2 GHz |

| Supplier Device Package | 770-FCBGA (23x23) |

| USB | USB 3.1 (1) |

| Voltage - I/O | 1.1 V, 1.8 V, 3.3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tape & Reel (TR) | 250 | $ 73.23 | |

| Texas Instruments | LARGE T&R | 1 | $ 85.34 | |

| 100 | $ 75.86 | |||

| 250 | $ 62.36 | |||

| 1000 | $ 55.78 | |||

Description

General part information

AM68 Series

The AM68 scalable processor family is based on the evolutionary Jacinto™ 7 architecture, targeted at Smart Vision Camera and General Compute applications and built on extensive market knowledge accumulated over a decade of TI’s leadership in the Vision processor market. The AM68x family is built for a broad set of cost-sensitive high-performance compute applications in Factory Automation, Building Automation, and other markets.

The AM68 provides high performance compute technology for both traditional and deep learning algorithms at industry leading power/performance ratios with a high level of system integration to enable scalability and lower costs for advanced vision camera applications. Key cores include the latest Arm and GPU processors for general compute, next generation DSP with scalar and vector cores, dedicated deep learning and traditional algorithm accelerators, an integrated next generation imaging subsystem (ISP), video codec, and isolated MCU island. All protected by industrial-grade safety and security hardware accelerators.

General Compute Cores and Integration Overview: Separate dual core cluster configuration of Arm® Cortex®-A72 facilitates multi-OS applications with minimal need for a software hypervisor. Up to two Arm® Cortex®-R5F subsystems enable low-level, timing critical processing tasks to leave the Arm® Cortex®-A72 core’s unencumbered for applications. Building on the existing world-class ISP, TI’s 7th generation ISP includes flexibility to process a broader sensor suite, support for higher bit depth, and features targeting analytics applications. Integrated diagnostics and safety features support operations up to SIL-2 levels while the integrated security features protect data against modern day attacks. CSI2.0 ports enable multi sensor inputs.

Documents

Technical documentation and resources