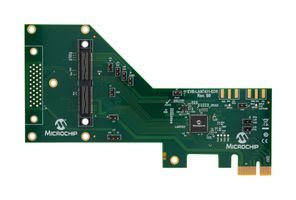

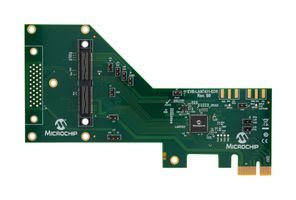

EVB-LAN7431-EDS

ActiveEVAL BRD, PCIE 3.1 RGMII GIGABIT BRIDGE ROHS COMPLIANT: YES

Deep-Dive with AI

Search across all available documentation for this part.

EVB-LAN7431-EDS

ActiveEVAL BRD, PCIE 3.1 RGMII GIGABIT BRIDGE ROHS COMPLIANT: YES

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | EVB-LAN7431-EDS |

|---|---|

| Function | Ethernet |

| Secondary Attributes | Graphical User Interface (GUI) |

| Supplied Contents | Board(s) |

| Type | Interface |

| Utilized IC / Part | LAN7431 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

Description

General part information

LAN7431 Series

Microchip's LAN7431 is a PCIe 3.1 (at 2.5GT/s) to Reduced Gigabit Media Independent Interface (RGMII) Gigabit Networking bridge providing an ultra-high-performance and cost-effective PCIe to Ethernet connectivity solution. LAN7431 contains an integrated RGMII interface, PCIe PHY, PCIe endpoint controller, 10/100/1000 Gigabit Ethernet MAC, Integrated OTP, JTAG TAP and EEPROM controller.

PCIe-based networking provides flexibility for the routing and placement of network connections anywhere in the system. Specific enhancements for PCIe LPSS (Low Power Sub-States) L1.1 and LPSS L1.2 have been integrated to lower system power consumption. LAN7431 is available with a wide range of drivers including Windows®, Linux®, and Pseudo Code for development towards RTOS. LAN7431 also supports Precision Time Protocol using industry standard 1588-2008 PTP. GPIOs are provided that can be software defined for this function. Included within this feature is a programmable timer compare output that can also be software configured.

The LAN7431 integrates all needed voltage regulators and requires only a single 3.3V supply. Further BOM savings can be realized through the integrated clock tree only requiring one external crystal or clock source. An EEPROM interface is provided although is not mandatory - an integrated OTP memory can provide for configuration data, further reducing system design cost and burden.

Documents

Technical documentation and resources