SPC565MZP56D

NRNDNXP 32-BIT MCU, POWER ARCH CORE, 1MB FLASH, 40MHZ, -40/+125DEGC, AUTOMOTIVE GRADE, PBGA 388/ TRAY ROHS COMPLIANT: YES

Deep-Dive with AI

Search across all available documentation for this part.

SPC565MZP56D

NRNDNXP 32-BIT MCU, POWER ARCH CORE, 1MB FLASH, 40MHZ, -40/+125DEGC, AUTOMOTIVE GRADE, PBGA 388/ TRAY ROHS COMPLIANT: YES

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | SPC565MZP56D |

|---|---|

| A/D Channels | 40 count |

| A/D Resolution (bits) | 10 bit |

| Connectivity | USART, CANbus, UART, SCI, EBI, SPI, EMI |

| Core Configuration | Single-Core |

| Core Processor | PowerPC |

| Core Size (Bit Width) | 32 Bit |

| Mounting Type | Surface Mount |

| Number of I/O | 56 |

| Operating Temperature (Max) | 125 °C |

| Operating Temperature (Min) | -40 °C |

| Oscillator Type | External |

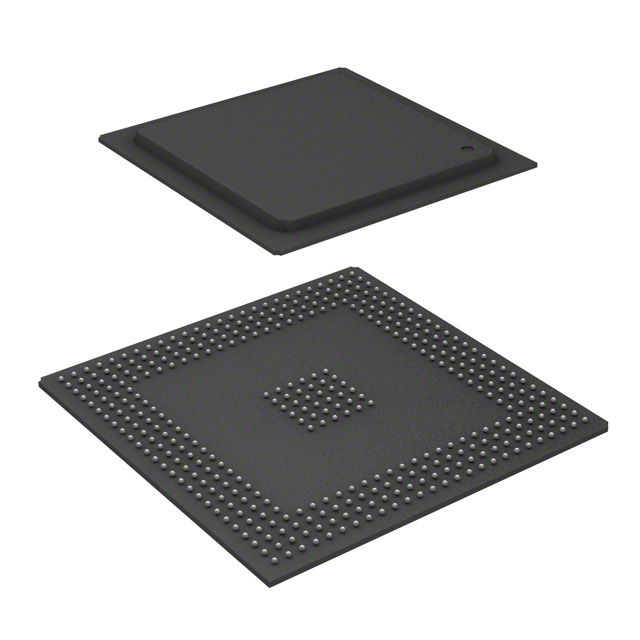

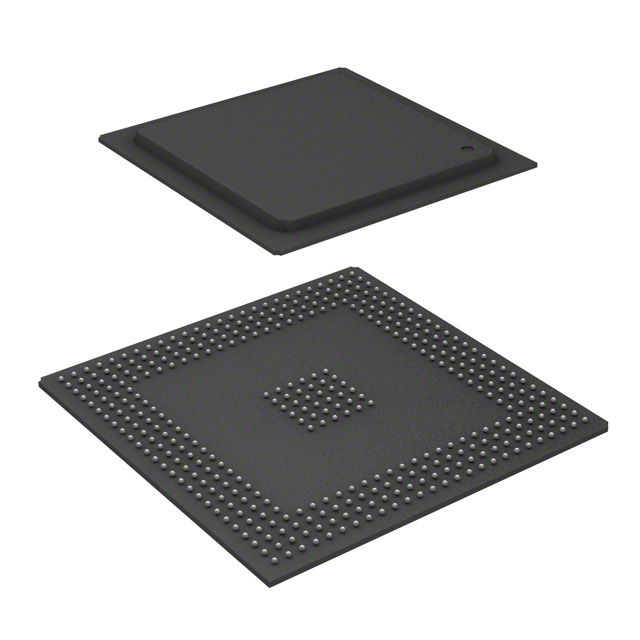

| Package / Case | 388-BBGA |

| Package Length | 27 mm |

| Package Name | 388-PBGA |

| Package Width | 27 mm |

| Peripherals | WDT, POR, PWM |

| Program Memory Depth | 1 M |

| Program Memory Size | 1 MB |

| Program Memory Type | FLASH |

| Program Memory Width | 8 bit |

| RAM Size Depth | 36 K |

| RAM Size Width | 8 bit |

| Speed | 56 MHz |

| Voltage - Supply (Vcc/Vdd) Maximum | 2.7 V |

| Voltage - Supply (Vcc/Vdd) Minimum | 2.5 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

CAD

3D models and CAD resources for this part

Description

General part information

SPC565 Series

An MPC500 core with a floating point unit (FPU) and a burst buffer controller (BBC)

Unified system integration unit (USIU), a flexible memory controller, and enhanced interrupt controller

1 Mbyte of Flash memory (UC3F)Typical endurance of 100,000 write/erase cycles @ 25ºCTypical data retention of 100 years @ 25ºC

Documents

Technical documentation and resources