ADAU1860/ADAU1860-1 Series

Three ADCs, One DAC, Low Power Codec with Audio DSPs

Manufacturer: Analog Devices

Catalog

Three ADCs, One DAC, Low Power Codec with Audio DSPs

Key Features

• Programmable FastDSP audio processing engineUp to 768 kHz sample rateBiquad filters, limiters, volume controls, mixing

• Up to 768 kHz sample rate

• Biquad filters, limiters, volume controls, mixing

• Tensilica HiFi 3z DSP coreQuad MAC per cycle: 24 x 24-bit multiplier and 64-bit accumulatorFlexible power operation mode: 24.576 MHz, 49.152 MHz, 73.728 MHz, and 98.304 MHz288 kB total memoryJTAG debug and trace

• Quad MAC per cycle: 24 x 24-bit multiplier and 64-bit accumulator

• Flexible power operation mode: 24.576 MHz, 49.152 MHz, 73.728 MHz, and 98.304 MHz

• 288 kB total memory

• JTAG debug and trace

• Low latency, 24-bit ADCs and DAC106 dB SNR (signal through ADC with A-weighted filter)110 dB combined SNR (signal through DAC and headphone with A-weighted filter)

• 106 dB SNR (signal through ADC with A-weighted filter)

• 110 dB combined SNR (signal through DAC and headphone with A-weighted filter)

• Programmable double precision MAC engine for maximum 24-stage equalizer

• Serial port sample rates from 8 kHz to 768 kHz

• 5 μs group delay (fS= 768 kHz) analog in to analog out with FastDSP bypass (zero instructions)

• 3 differential or single-ended analog inputs, configurable as microphone or line inputs

• 8 digital microphone inputs

• Analog differential audio output, configurable as either line output or headphone drive

• 2 PDM output channels

• PLL supporting any input clock rate from 30 kHz to 36 MHz

• 4 channel asynchronous sample rate converters (ASRCs)

• 2, 16-channel serial audio ports supporting I2S, left justified, right justified, or up to TDM16 (TDM12 in Turbo mode)

• 8 interpolators and 8 decimators with flexible routing

• Power suppliesDigital I/O IOVDD at 1.1 V to 1.98 VDigital DVDD at 0.85 V to 1.21 VHeadphone HPVDD at 1.8 V typicalHeadphone HPVDD_L at 1.2 V to HPVDD

• Digital I/O IOVDD at 1.1 V to 1.98 V

• Digital DVDD at 0.85 V to 1.21 V

• Headphone HPVDD at 1.8 V typical

• Headphone HPVDD_L at 1.2 V to HPVDD

• Control/communication interfacesI2C, SPI, or UART control portsMaster quad SPI (QSPI)UART communication port

• I2C, SPI, or UART control ports

• Master quad SPI (QSPI)

• UART communication port

• Self-boot from QSPI flash

• Flexible GPIO and IRQ

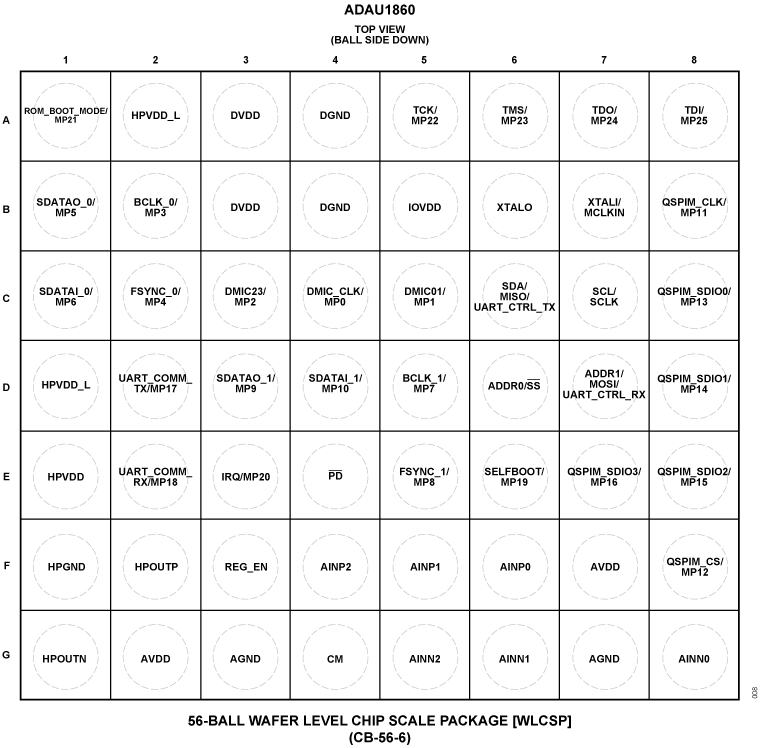

• 56-ball, 0.35 mm pitch, 2.980 mm × 2.679 mm WLCSP

Description

AI

The ADAU1860/ADAU1860-1 are codecs with three inputs and one output that incorporate two digital signal processors (DSPs). The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise canceling earphones. With the addition of just a few passive components, the ADAU1860/ADAU1860-1 provide a complete earphone solution.APPLICATIONSNoise canceling handsets, headsets, and headphonesBluetooth active noise canceling (ANC) handsets, headsets, and headphonesPersonal navigation devicesDigital still and video camerasMusical instrument effect processorsMultimedia speaker systemsSmartphones