Catalog

14-Bit, 500 MSPS LVDS, Dual Analog-to-Digital Converter

Key Features

• LVDS digital outputs

• 1.1 W total power per channel at 500MSPS (default settings)

• SFDR = 85 dBc at 170MHz fIN(500MSPS)

• SNR = 68.6 dBFS at 170MHz fIN(500MSPS)

• ENOB = 10.9 bits at 170 MHz fIN

• DNL = ±0.5 LSB

• INL = ±2.5 LSB

• Noise Density = -153 dBFS/Hz at 500 MSPS

• 1.25V, 2.50 V and 3.3V supply operation

• No missing codes

• Internal analog-to-digital converter (ADC) voltage reference

• See data sheet for additional features

Description

AI

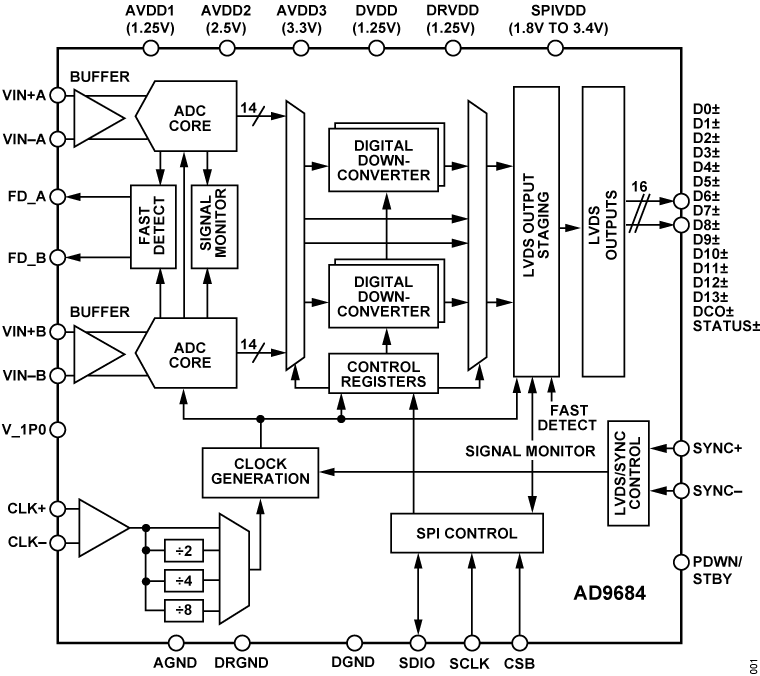

The AD9684 is a dual, 14-bit, 500 MSPS ADC. The device has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed for sampling wide bandwidth analog signals. The AD9684 is optimized for wide input bandwidth, a high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth buffered inputs, supporting a variety of user selectable input ranges. An integrated voltage reference eases design considerations. Each ADC data output is internally connected to an optional decimate by 2 block.The analog input and clock signals are differential inputs. Each ADC data output is internally connected to two digital downconverters (DDCs). Each DDC consists of four cascaded signal processing stages: a 12-bit frequency translator (NCO), and three half-band decimation filters supporting a divide by factor of two, four, and eight.ApplicationsCommunicationsDiversity multi-band, multi-mode digital receivers3G/4G, TD-SCDMA, WCDMA, MC-GSM, LTEGeneral-purpose software radiosUltrawideband satellite receiverInstrumentation (spectrum analyzers, network analyzers, integrated RF test solutions)RadarDigital oscilloscopesHigh speed data acquisition systemsDOCSIS CMTS upstream receive pathsHFC digital reverse path receivers