TS2PCIE2212 Series

Manufacturer: Texas Instruments

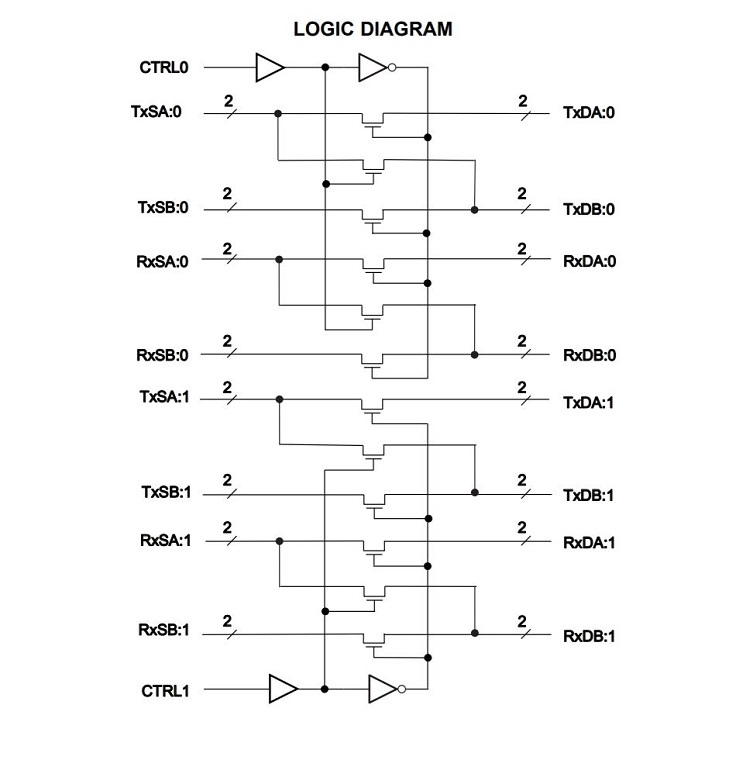

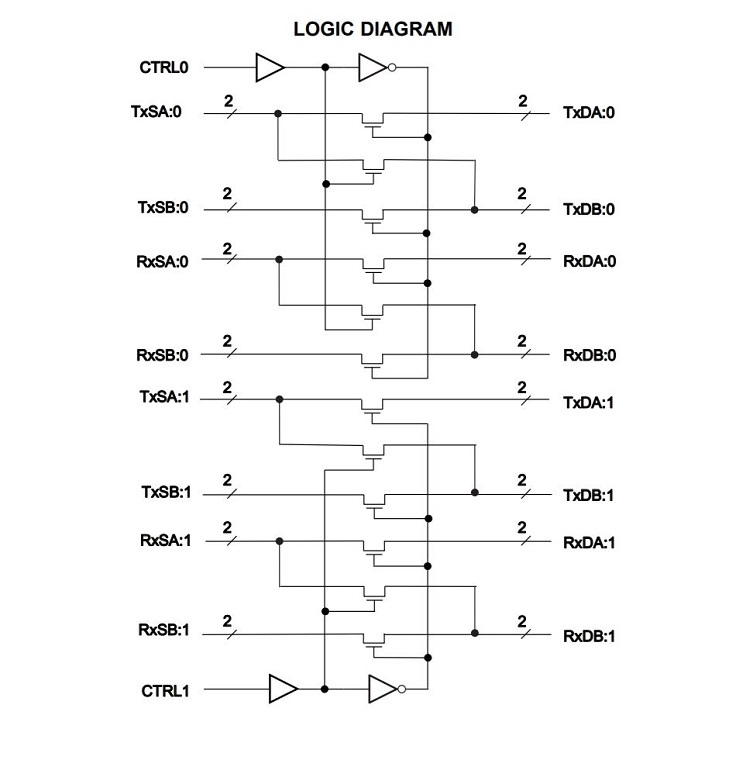

4-CHANNEL PCIE 2:1 MULTIPLEXER/DEMULTIPLEXER PASSIVE FET SWITCH

| Part | On-State Resistance (Max) [Max] | Applications | Mounting Type | Supplier Device Package | Multiplexer/Demultiplexer Circuit | Number of Channels | Voltage - Supply, Single (V+) [Min] | Voltage - Supply, Single (V+) [Max] | Operating Temperature [Min] | Operating Temperature [Max] | Package / Case |

|---|---|---|---|---|---|---|---|---|---|---|---|

Texas Instruments | 17 Ohms | PCI Express® | Surface Mount | 48-NFBGA (5x5) | 2:1 | 2 | 1.7 V | 1.9 V | 0 °C | 85 C | 48-TFBGA |

Texas Instruments | 17 Ohms | PCI Express® | Surface Mount | 48-NFBGA (5x5) | 2:1 | 2 | 1.7 V | 1.9 V | 0 °C | 85 C | 48-TFBGA |