AD9152 Series

Dual, 16-Bit, 2.25 GSPS, TxDAC+ Digital-to-Analog Converter

Manufacturer: Analog Devices

Catalog

Dual, 16-Bit, 2.25 GSPS, TxDAC+ Digital-to-Analog Converter

Key Features

• Supports input data rates up to 1.125 GSPS

• Proprietary low spurious and distortion designSingle carrier LTE 20 MHz bandwidth (BW), ACLR = 77 dBcat 180 MHz IFSFDR = 72 dBc at 150 MHz IF, −6 dBFS

• Single carrier LTE 20 MHz bandwidth (BW), ACLR = 77 dBcat 180 MHz IF

• SFDR = 72 dBc at 150 MHz IF, −6 dBFS

• Flexible 4-lane JESD204B interface

• Multiple chip synchronizationFixed latencyData generator latency compensation

• Fixed latency

• Data generator latency compensation

• Selectable 1×, 2×, 4×, and 8× interpolation filterLow power architecture

• Low power architecture

• Input signal power detectionEmergency stop for downstream analog circuitry protection

• Emergency stop for downstream analog circuitry protection

• Transmit enable function allows extra power saving

• High performance, low noise, phase-locked loop (PLL) clock multiplier

• Digital inverse sinc filter and programmable finite impulse response (FIR) filter

• Low power: 1223 mW at 1.5 GSPS, 1406 mW at 2.0 GSPS, full operating conditions

• 56-lead LFCSP with exposed pad

Description

AI

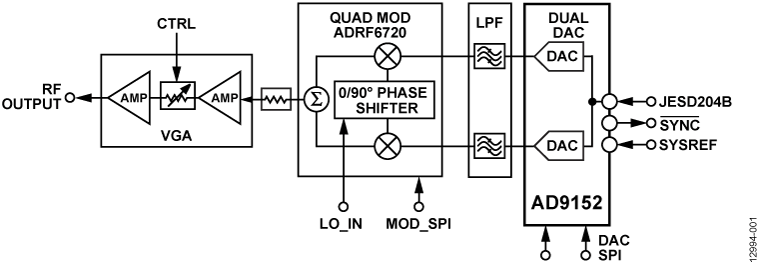

The AD9152 is a dual, 16-bit, high dynamic range digital-to-analog converter (DAC) that provides a maximum sample rate of 2.25 GSPS, permitting a multicarrier generation up to the Nyquist frequency. The DAC outputs are optimized to interface seamlessly with the ADRF6720 analog quadrature modulator (AQM) from Analog Devices, Inc. An optional 3-wire or 4-wire serial port interface (SPI) provides for programming/readback of many internal parameters. The full-scale output current can be programmed over a range of 4 mA to 20 mA. The AD9152 is available in a 56-lead LFCSP. The AD9152 is a member of the TxDAC+®family.PRODUCT HIGHLIGHTSUltrawide signal bandwidth enables emerging wideband and multiband wireless applications.Advanced low spurious and distortion design techniques provide high quality synthesis of wideband signals from baseband to high intermediate frequencies.JESD204B Subclass 1 support simplifies multichip synchronization in software and hardware design.Fewer pins for data interface width with the serializer/deserializer (SERDES) JESD204B four-lane interface.Programmable transmit enable function allows easy design balance between power consumption and wake-up time.Small package size with an 8 mm × 8 mm footprint.APPLICATIONSWireless communicationsMulticarrier LTE and GSM base stationsWideband repeatersSoftware defined radiosWideband communicationsPoint to point microwave radiosLMDS/MMDSTransmit diversity, multiple input/multiple output (MIMO)InstrumentationAutomated test equipment