AD9083 Series

16-Channel, 125 MHz Bandwidth, JESD204B Analog-to-Digital Converter

Manufacturer: Analog Devices

Catalog

16-Channel, 125 MHz Bandwidth, JESD204B Analog-to-Digital Converter

Key Features

• 1.0 V and 1.8 V supply operation

• 125 MHz usable analog input bandwidth

• Sample rate up to 2 GSPS

• Noise spectral density in 100 MHz bandwidth = −145 dBFS/Hz, 2.0 GSPS encode

• SNR = 66 dBFS in 100 MHz bandwidth, 2.0 GSPS encode

• SNR = 82 dBFS in 15.625 MHz bandwidth, 2.0 GSPS encode

• SFDR = 60 dBc in 100 MHz bandwidth, 2.0 GSPS encode

• SFDR = 80 dBc in 15.625 MHz bandwidth, 2.0 GSPS encode

• Large signal dither

• 90 mW total power per channel at 2.0 GSPS (default settings), 35 mW power per channel (min)

• Flexible input range: 0.5 V p-p to 2 V p-p differential

• 90 dB channel crosstalk, 2.0 GSPS encode

• Digital processorCIC decimation filterProgrammable DDCData gating

• CIC decimation filter

• Programmable DDC

• Data gating

• JESD204B subclass 1 encoded outputsSupports up to 16Gbps/laneFlexible sample data processingFlexible JESD204B lane configurations

• Supports up to 16Gbps/lane

• Flexible sample data processing

• Flexible JESD204B lane configurations

• Serial port control

Description

AI

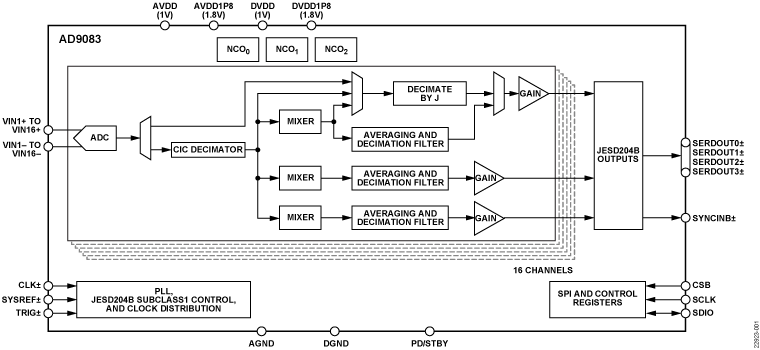

The AD9083 is a 16-channel, 125 MHz bandwidth, continuous time Σ-Δ (CTSD) ADC. The device features an on-chip, programmable, single-pole antialiasing filter and termination resistor that is designed for low power, small size, and ease of use.The 16 ADC cores features a first-order, CTSD modulator architecture with integrated, background nonlinearity correction logic and self cancelling dither. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.The analog input and clock signals are differential inputs. Each ADC has a signal processing tile to filter out of band shaped noise from the Σ-Δ ADC and reduce the sample rate. Each tile contains a cascaded integrator comb (CIC) filter, a quadrature digital downconverter (DDC) with multiple finite input response (FIR) decimation filters (decimate by J block), or up to three quadrature DDC channels with averaging decimation filters for data gating applications.Users can configure the Subclass 1 JESD204B based, high speed serialized output in a variety of lane configurations (up to four), depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF±, TRIG±, and SYNCINB± input pins.The AD9083 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V capable 3-wire serial port interface (SPI).The AD9083 is available in a Pb-free, 100-ball CSP_BGA and is specified over the −40°C to +85°C industrial temperature range.This product is protected by a US patent.APPLICATIONSMillimeter wave imagingElectronic beam forming and phased arraysMultichannel wideband receiversElectronic support measuresPRODUCT HIGHLIGHTSContinuous time, Σ-Δ analog-to-digital converters (ADCs) support signal bandwidths of up to 125 MHz with low power and minimal filtering.Integrated digital processing blocks reduce data payload and lower overall system cost.Configurable JESD204B interface reduces printed circuit board (PCB) complexity.Flexible power-down options.SPI interface controls various product features and functions to meet specific system requirements.Small, 9 mm × 9 mm, 100-ball CSP_BGA package, simple interface, and integrated digital processing save PCB space.