ADN4621 Series

7.5 kV RMS/3.75 kV RMS, Dual-Channel LVDS 2.5 Gigabit Isolator (1 Reverse Channel)

Manufacturer: Analog Devices

Catalog

7.5 kV RMS/3.75 kV RMS, Dual-Channel LVDS 2.5 Gigabit Isolator (1 Reverse Channel)

Key Features

• 7.5 kV rms/3.75 kV rms LVDS isolators

• Complies with TIA/EIA-644-A LVDS signal levels

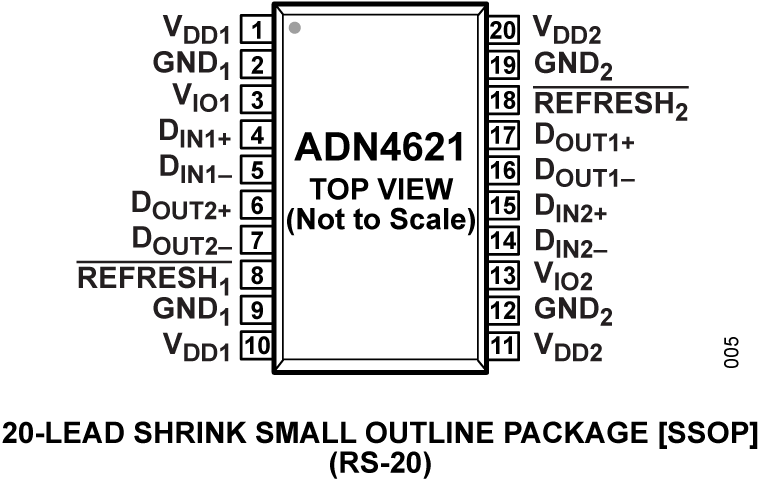

• Dual-channel configuration (ADN4620: 2 + 0, ADN4621: 1 + 1)

• Any data rate up to 2.5 Gbps switching with low jitter5 Gbps total bandwidth across two channels2.15 ns typical propagation delayTypical jitter: 0.82 ps rms random, 40 ps total peak-to-peak

• 5 Gbps total bandwidth across two channels

• 2.15 ns typical propagation delay

• Typical jitter: 0.82 ps rms random, 40 ps total peak-to-peak

• Lower power 1.8 V supplies with 3.3 V supplies for I/O

• Up to ±8 kV IEC 61000-4-2 ESD protection across isolation barrier

• High common-mode transient immunity: 70 kV/μs typical

• Safety and regulatory approvals (16-lead SOIC_IC package)UL (pending): 7500 V rms for 1 minute per UL 1577CSA Component Acceptance Notice 5A (pending)VDE certificate of conformity, reinforced insulation (pending)DIN V VDE V 0884-11 (VDE V 0884-11):2017-01VIORM= 1500 VPEAK(maximum working insulation voltage)

• UL (pending): 7500 V rms for 1 minute per UL 1577

• CSA Component Acceptance Notice 5A (pending)

• VDE certificate of conformity, reinforced insulation (pending)DIN V VDE V 0884-11 (VDE V 0884-11):2017-01VIORM= 1500 VPEAK(maximum working insulation voltage)

• DIN V VDE V 0884-11 (VDE V 0884-11):2017-01

• VIORM= 1500 VPEAK(maximum working insulation voltage)

• Enable or disable refresh (20-lead SSOP package)

• Operating temperature range: −40°C to +125°C

• Compact SSOP package with 5.3 mm creepage or wide SOIC_IC package with 15.1 mm creepage

Description

AI

TheADN4620/ADN4621 are dual-channel, signal isolated, low voltage differential signaling (LVDS) buffers that operate at up to 2.5 Gbps with very low jitter. The devices integrate Analog Devices, Inc.,iCoupler®technology, enhanced for high speed operation to provide drop-in galvanic isolation of LVDS signal chains. AC coupling and/or level shifting to the LVDS receivers and from the LVDS drivers allows isolation of other high speed signals, such as current mode logic (CML).The ADN4620/ADN4621 include a refresh mechanism to monitor the input and output states and ensure that they remain the same in the absence of data transitions (for example, at power-on). For lower power consumption and high speed operation with low jitter, the isolator circuits rely on 1.8 V supplies, while 3.3 V supplies are used for LVDS receivers to support the full common-mode range with an input voltage range (input common mode plus differential input voltage) of 0 V to 2.4 V per Table 2 in the data sheet.The devices are fully specified over a wide industrial temperature range and are available in a compact SSOP package with 5.3 mm creepage (for reinforced insulation at ac mains voltages) or a wide SOIC_IC package with 15.1 mm creepage (for high working insulation voltages up to 1500 V peak, reinforced).APPLICATIONSAnalog front-end isolationData plane isolationIsolated high speed clock and data linksMultigigabit serialization/deserialization (SERDES)PCB-to-PCB optical replacement (for example, short reach fiber)Protected by U.S. Patents 7,075,329; 9,941,565; and 10,205,442. Other patents are pending.