70121L25JG

ObsoleteIC SRAM 18KBIT PARALLEL 52PLCC

Deep-Dive with AI

Search across all available documentation for this part.

70121L25JG

ObsoleteIC SRAM 18KBIT PARALLEL 52PLCC

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 70121L25JG |

|---|---|

| Access Time | 25 ns |

| Memory Format | SRAM |

| Memory Interface | Parallel |

| Memory Organization [custom] | 9 bit |

| Memory Organization [custom] | 2 K |

| Memory Size | 18 Kbit |

| Memory Type | Volatile |

| Mounting Type | Surface Mount |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Package / Case | 52-LCC (J-Lead) |

| Supplier Device Package | 52-PLCC (19.13x19.13) |

| Technology | SRAM - Dual Port, Asynchronous |

| Voltage - Supply [Max] | 5.5 V |

| Voltage - Supply [Min] | 4.5 V |

| Write Cycle Time - Word, Page | 25 ns |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | N/A | 0 | $ 24.14 | |

Description

General part information

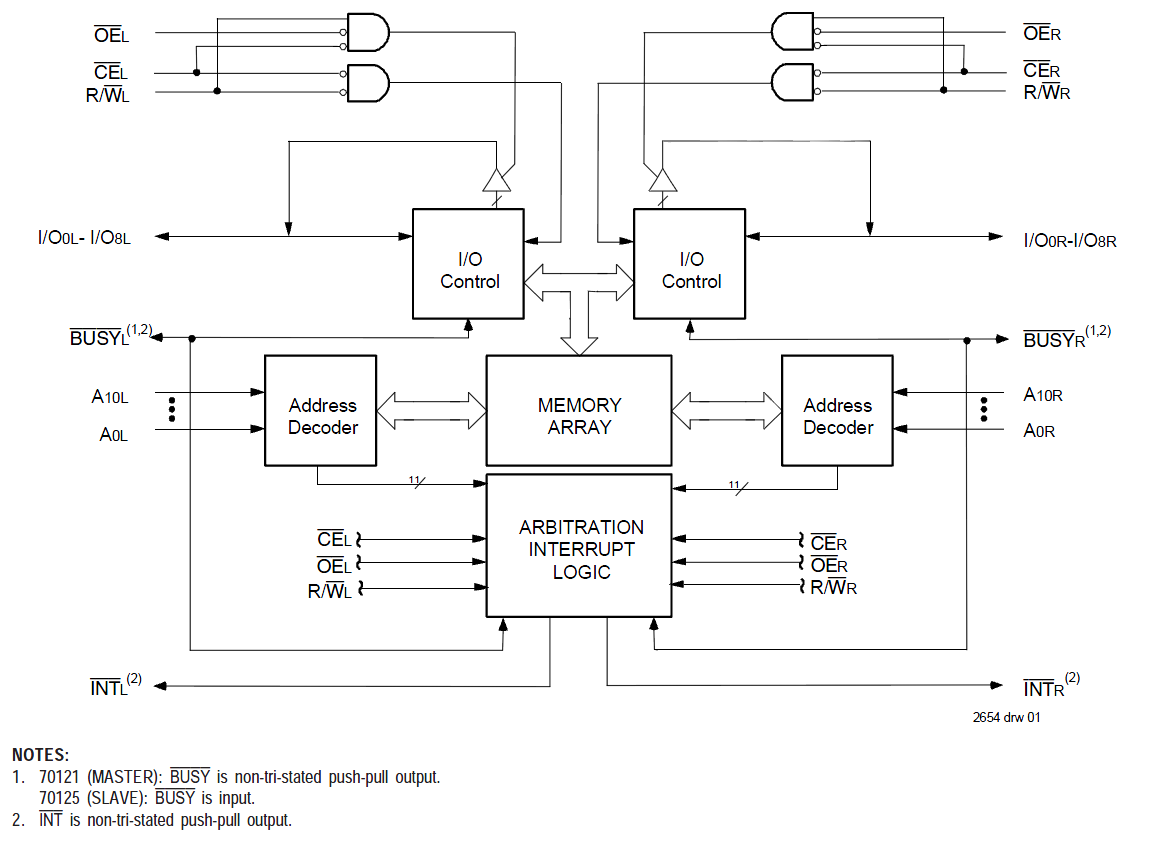

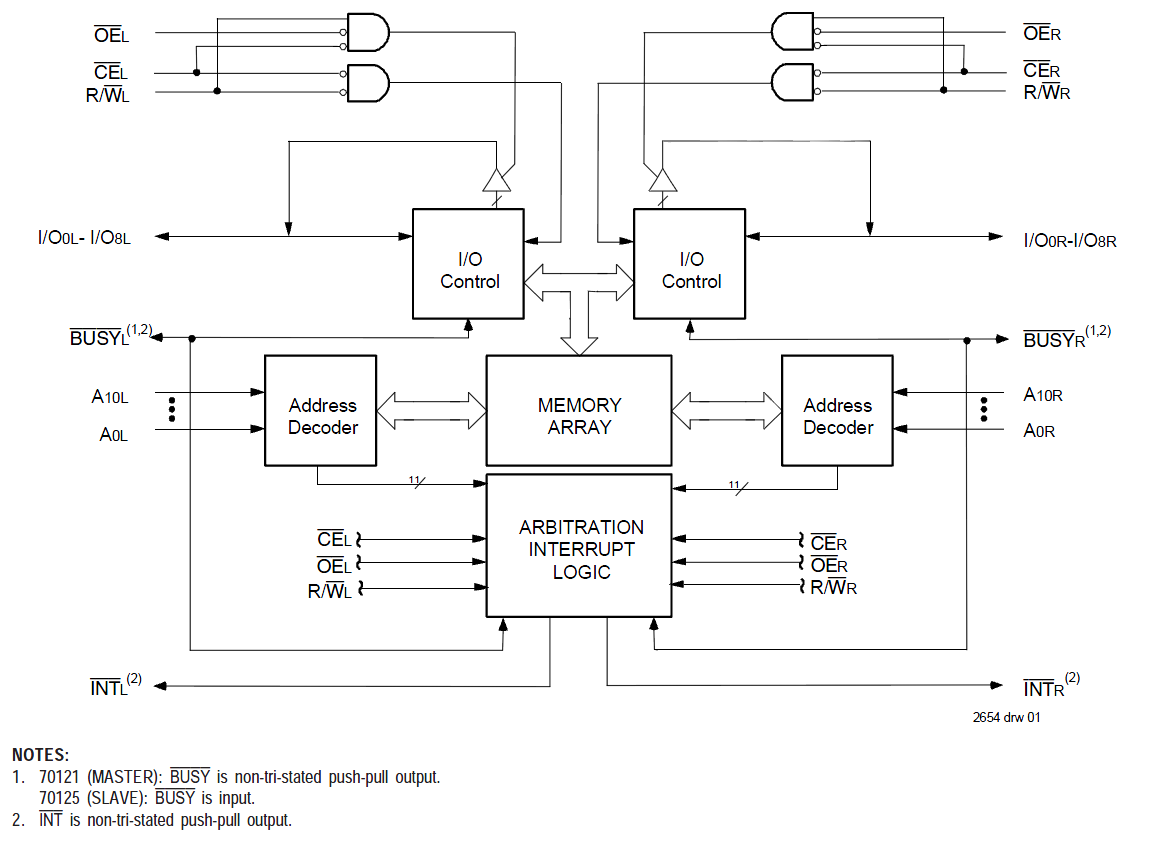

70121 Series

The 70121 is a high-speed 2K x 9 Dual-Port Static RAM designed to be used as a stand-alone 9-bit Dual- Port RAM or as a "MASTER" Dual-Port RAM together with the 70125 "SLAVE" Dual-Port in 18-bit-or-more word width systems. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 18-bit-or-wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic. An automatic power-down feature, controlled by CE, permits the on-chip circuitry of each port to enter a very low standby power mode.

Documents

Technical documentation and resources