HIP2210FRTZ-T7A

Obsolete100V, 3A SOURCE, 4A SINK, HIGH FREQUENCY HALF-BRIDGE DRIVERS WITH TRI-LEVEL PWM INPUT AND ADJUSTABLE DEAD TIME

Deep-Dive with AI

Search across all available documentation for this part.

HIP2210FRTZ-T7A

Obsolete100V, 3A SOURCE, 4A SINK, HIGH FREQUENCY HALF-BRIDGE DRIVERS WITH TRI-LEVEL PWM INPUT AND ADJUSTABLE DEAD TIME

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | HIP2210FRTZ-T7A |

|---|---|

| Channel Type | Synchronous |

| Current - Peak Output (Source, Sink) [custom] | 3 A |

| Current - Peak Output (Source, Sink) [custom] | 4 A |

| Driven Configuration | Half-Bridge |

| Gate Type | N-Channel MOSFET |

| High Side Voltage - Max (Bootstrap) [Max] | 115 V |

| Input Type | Non-Inverting |

| Logic Voltage - VIL, VIH [custom] | 1.47 V |

| Logic Voltage - VIL, VIH [custom] | 1.84 V |

| Mounting Type | Surface Mount |

| Number of Drivers | 2 |

| Operating Temperature [Max] | 125 ¯C |

| Operating Temperature [Min] | -40 °C |

| Package / Case | 10-WDFN Exposed Pad |

| Supplier Device Package | 10-TDFN (4x4) |

| Voltage - Supply [Max] | 18 V |

| Voltage - Supply [Min] | 6 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Cut Tape (CT) | 1 | $ 3.15 | |

| 10 | $ 2.05 | |||

| 25 | $ 1.76 | |||

| 100 | $ 1.44 | |||

| Digi-Reel® | 1 | $ 3.15 | ||

| 10 | $ 2.05 | |||

| 25 | $ 1.76 | |||

| 100 | $ 1.44 | |||

Description

General part information

HIP2210 Series

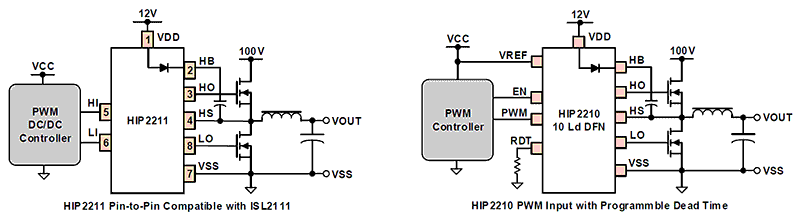

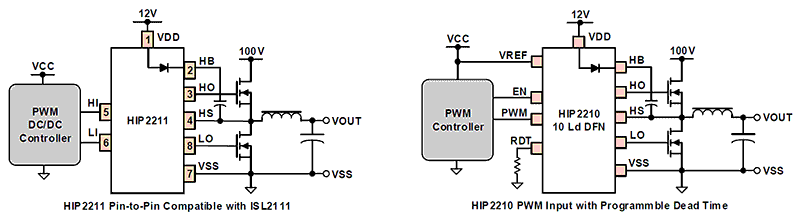

The HIP2210 is a 100V, 3A source, 4A sink high-frequency half-bridge NMOS FET driver. The HIP2210 features a tri-level PWM input with programmable dead time. Its wide operating supply range of 6V to 18V and integrated high-side bootstrap diode supports driving the high-side and low-side NMOS in 100V half-bridge applications.

This driver features strong 3A source, 4A sink drivers with very fast 15ns typical propagation delay and 2ns typical delay matching, making it optimal for high-frequency switching applications. VDD and boot UVLO protects against an undervoltage operation.

The tri-level input of the HIP2210 PWM pin controls the high-side and low-side drivers with a single pin. When the PWM input is at logic high, the high-side bridge FET is turned on and the low-side FET is off. When the input is at logic low, the low-side bridge FET is turned on and the high-side FET is turned off. When the input voltage is in the mid-level state, both the high-side and low-side bridge FETs are turned off. The PWM threshold levels are proportional to an external input reference voltage on the VREF pin, allowing PWM operation across a 2.7V to 5.5V logic range.

Documents

Technical documentation and resources