74LVCH16374APAG8

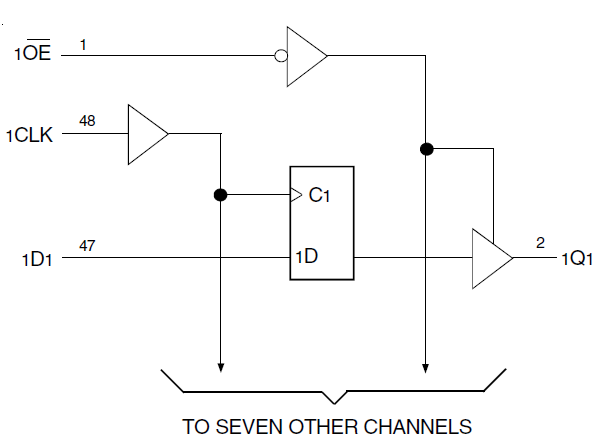

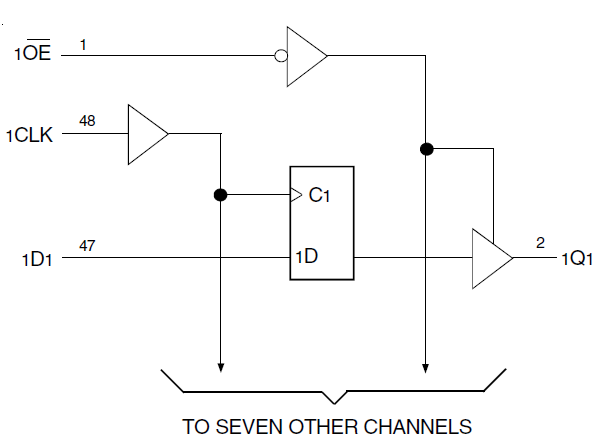

Obsolete3.3V CMOS 16-BIT EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5.0V TOLERANT I/O, AND BUS-HOLD

Deep-Dive with AI

Search across all available documentation for this part.

74LVCH16374APAG8

Obsolete3.3V CMOS 16-BIT EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS, 5.0V TOLERANT I/O, AND BUS-HOLD

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 74LVCH16374APAG8 |

|---|---|

| Clock Frequency | 150 MHz |

| Current - Output High, Low | 24 mA |

| Current - Quiescent (Iq) | 10 µA |

| Function | Standard |

| Input Capacitance | 4.5 pF |

| Max Propagation Delay @ V, Max CL | 4.5 ns |

| Mounting Type | Surface Mount |

| Number of Bits per Element | 8 |

| Number of Elements | 2 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output Type | Tri-State, Non-Inverted |

| Package / Case | 48-TFSOP |

| Package / Case | 0.24 in |

| Package / Case [custom] | 6.1 mm |

| Supplier Device Package | 48-TSSOP |

| Trigger Type | Positive Edge |

| Type | D-Type |

| Voltage - Supply [Max] | 3.6 V |

| Voltage - Supply [Min] | 2.7 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

74LVCH16374A Series

The 74LVCH16374A 16-bit edge-triggered D-type register is ideal for use as a buffer register for data synchronization and storage. Flow-through organization of signal pins simplifies layout. All pins of the 74LVCH16374A can be driven from either 3.3V or 5V devices which allows the use of this device as a translator in a mixed 3.3V/5V supply system. The 74LVCH16374A has "bus-hold" which prevents floating inputs and eliminates the need for pull-up/down resistors. The 74LVCH16374A operates at -40C to +85C

Documents

Technical documentation and resources