TSB41LV06APZP

ActiveIEEE 1394A 6-PORT CABLE TRANSCEIVER/ARBITER

Deep-Dive with AI

Search across all available documentation for this part.

TSB41LV06APZP

ActiveIEEE 1394A 6-PORT CABLE TRANSCEIVER/ARBITER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | TSB41LV06APZP |

|---|---|

| Duplex | Half |

| Mounting Type | Surface Mount |

| Number of Drivers/Receivers [custom] | 2 |

| Number of Drivers/Receivers [custom] | 2 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

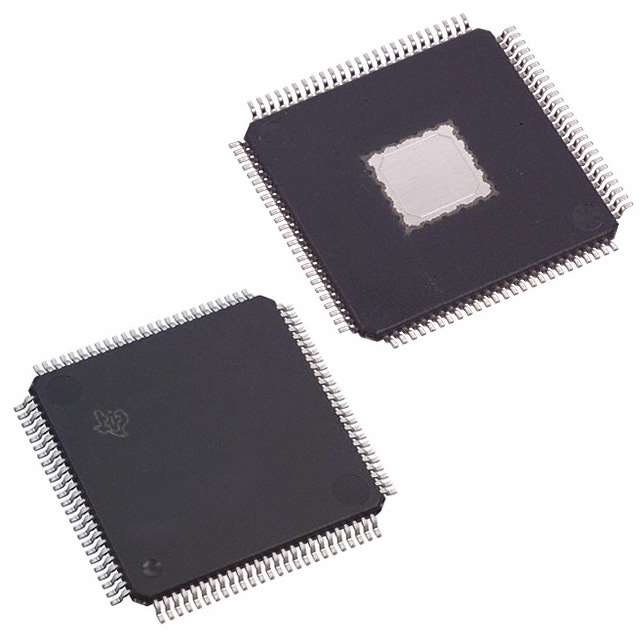

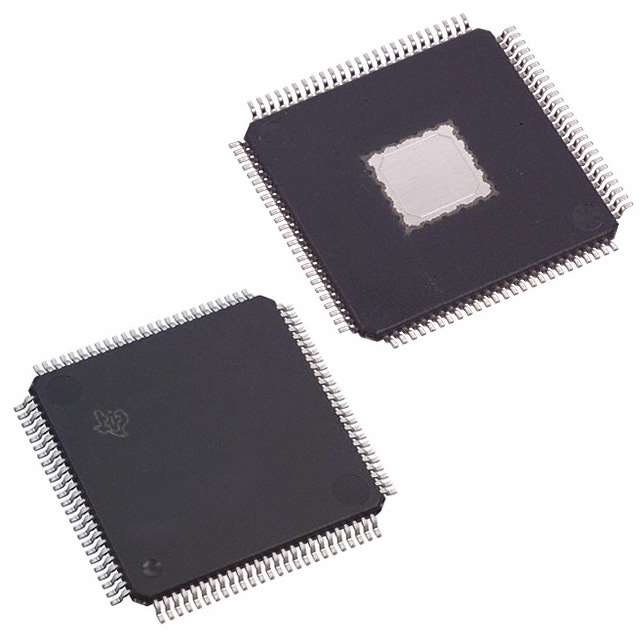

| Package / Case | 100-TQFP Exposed Pad |

| Protocol | IEEE 1394 |

| Supplier Device Package | 100-HTQFP (14x14) |

| Type | Transceiver |

| Voltage - Supply [Max] | 3.6 V |

| Voltage - Supply [Min] | 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | N/A | 13 | $ 18.86 | |

| 2776 | $ 18.86 | |||

| Tray | 1 | $ 11.48 | ||

| 10 | $ 10.55 | |||

| 25 | $ 10.11 | |||

| 90 | $ 9.62 | |||

| Texas Instruments | JEDEC TRAY (10+1) | 1 | $ 12.78 | |

| 100 | $ 11.16 | |||

| 250 | $ 8.61 | |||

| 1000 | $ 7.70 | |||

Description

General part information

TSB41LV06 Series

The TSB41LV06A provides the digital and analog transceiver functions needed to implement a six-port node in a cable-based IEEE 1394 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The TSB41LV06A is designed to interface with a link layer controller (LLC), such as the TSB12LV21, TSB12LV22, TSB12LV23, TSB12LV31, TSB12LV41, TSB12LV42, or TSB12LV01A.

The TSB41LV06A requires only an external 24.576 MHz crystal as a reference. An external clock may be provided instead of a crystal. An internal oscillator drives an internal phase-locked loop (PLL), which generates the required 393.216 MHz reference signal. This reference signal is internally divided to provide the clock signals used to control transmission of the outbound encoded strobe and data information. A 49.152 MHz clock signal is supplied to the associated LLC for synchronization of the two chips and is used for resynchronization of the received data. The power-down (PD) function, when enabled by asserting the PD terminal high, stops operation of the PLL.

The TSB41LV06A supports an optional isolation barrier between itself and its LLC. When the ISO\ input terminal is tied high, the LLC interface outputs behave normally. When the ISO\ terminal is tied low, internal differentiating logic is enabled, and the outputs are driven such that they can be coupled through a capacitive or transformer galvanic isolation barrier as described in Annex J of IEEE Std 1394-1995 and in the P1394a Supplement (section 5.9.4) (hereafter referred to as Annex J type isolation). To operate with TI bus holder isolation the ISO\ terminal on the PHY must be high.

Documents

Technical documentation and resources