542MLFT

ObsoleteCLOCK DRIVERS & DISTRIBUTION CLOCK DIVIDER

Deep-Dive with AI

Search across all available documentation for this part.

542MLFT

ObsoleteCLOCK DRIVERS & DISTRIBUTION CLOCK DIVIDER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 542MLFT |

|---|---|

| Differential - Input:Output [custom] | False |

| Differential - Input:Output [custom] | False |

| Frequency - Max [Max] | 156 MHz |

| Input | CMOS |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Output | CMOS, 3-State |

| Package / Case | 0.154 in |

| Package / Case | 8-SOIC |

| Package / Case | 3.9 mm |

| Ratio - Input:Output | 1:2 |

| Supplier Device Package | 8-SOIC |

| Type | Fanout Buffer (Distribution), Divider |

| Voltage - Supply [Max] | 5.5 V |

| Voltage - Supply [Min] | 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

Description

General part information

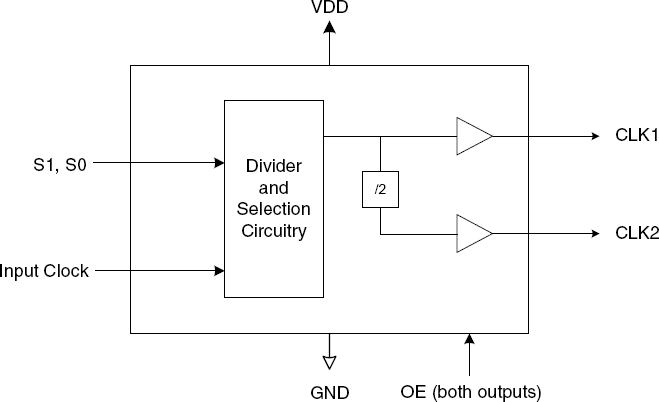

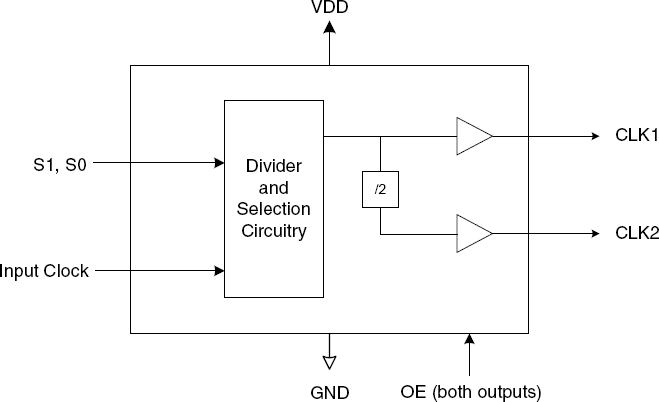

542 Series

The 542 is cost effective way to produce a high-quality clock output divided from a clock input. The chip accepts a clock input up to 156 MHz at 3.3 V and produces a divide by 2, 4, 6, 8, 12, or 16 of the input clock. There are two outputs on the chip, one being a low-skew divide by two of the other. For instance, if an 100 MHz input clock is used, the 542 can produce low-skew 50 MHz and 25 MHz clocks, or low skew 25 MHz and 12.5 MHz clocks. The chip has an all-chip power-down mode that stops the outputs low, and an OE pin that tri-states the outputs. See the 501, 502, 511, 512, and 525 for clock multipliers.

Documents

Technical documentation and resources