TLK10002CTR

ActiveDUAL-CHANNEL 10-GBPS MULTI-RATE TRANSCEIVER

Deep-Dive with AI

Search across all available documentation for this part.

TLK10002CTR

ActiveDUAL-CHANNEL 10-GBPS MULTI-RATE TRANSCEIVER

Technical Specifications

Parameters and characteristics for this part

| Specification | TLK10002CTR |

|---|---|

| Duplex | Full |

| Mounting Type | Surface Mount |

| Number of Drivers/Receivers [custom] | 2 |

| Number of Drivers/Receivers [custom] | 2 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

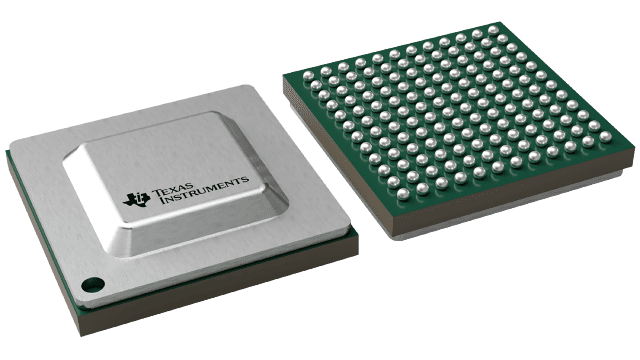

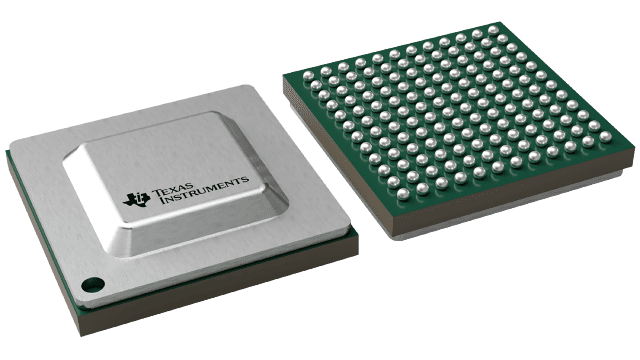

| Package / Case | FCBGA, 144-BBGA |

| Protocol | MDIO |

| Supplier Device Package | 144-FCBGA (13x13) |

| Type | Transceiver |

| Voltage - Supply [Max] | 1.89 V |

| Voltage - Supply [Min] | 1.71 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tray | 119 | $ 35.44 | |

| Texas Instruments | JEDEC TRAY (5+1) | 1 | $ 37.03 | |

| 100 | $ 32.91 | |||

| 250 | $ 27.06 | |||

| 1000 | $ 24.20 | |||

Description

General part information

TLK10002 Series

The TLK10002 device is a dual-channel, multi-rate transceiver intended for use in high-speed bidirectional point-to-point data transmission systems. It has special support for the wireless base station Remote Radio Head (RRH) application, but may also be used in other high-speed applications. It supports all the CPRI and OBSAI rates from 1.2288 Gbps to 9.8304 Gbps.

The TLK10002 performs 1:1, 2:1 and 4:1 serialization of the 8B/10B encoded data streams presented on its low-speed (LS) side data inputs. The serialized 8B/10B encoded data is presented on the high-speed (HS) side outputs. Likewise, the TLK10002 performs 1:1, 1:2 and 1:4 deserialization of 8B/10B encoded data streams presented on its high-speed side data inputs. The deserialized 8B/10B encoded data is presented on the low-speed side outputs. Depending on the serialization or deserialization ratio, the low-speed side data rate can range from 0.5 Gbps to 5 Gbps and the high-speed side data rate can range from 1 Gbps to 10 Gbps. Both low-speed and high-speed side data inputs and outputs are of differential current mode logic (CML) type with integrated termination resistors. In the 1:1 mode, the input can be raw (non-8B/10B encoded) data, allowing for transmission of PRBS data through the device.

The TLK10002 performs data serialization or deserialization and clock extraction as a physical layer interface device. Flexible clocking schemes are provided to support various operations. They include the support for clocking with an externally-jitter-cleaned clock recovered from the high-speed side.

Documents

Technical documentation and resources