M2051-11-625.0000

ObsoleteSAW PLL FOR 10GBE 64B/66B FEC

Deep-Dive with AI

Search across all available documentation for this part.

M2051-11-625.0000

ObsoleteSAW PLL FOR 10GBE 64B/66B FEC

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | M2051-11-625.0000 |

|---|---|

| Differential - Input:Output [custom] | True |

| Differential - Input:Output [custom] | True |

| Divider/Multiplier | Yes/No |

| Frequency - Max [Max] | 625 MHz |

| Input | LVCMOS, LVTTL, LVPECL, LVDS |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Output | LVPECL |

| Package / Case | 36-CLCC |

| PLL | True |

| Ratio - Input:Output [custom] | 2:2 |

| Supplier Device Package | 36-CLCC (9x9) |

| Voltage - Supply | 3.3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

M2051 Series

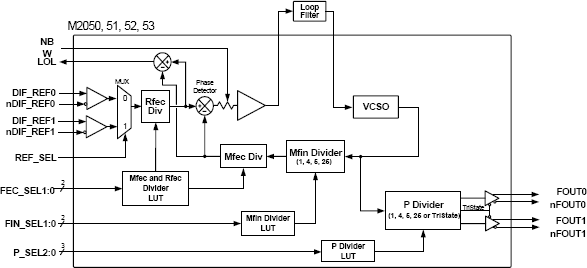

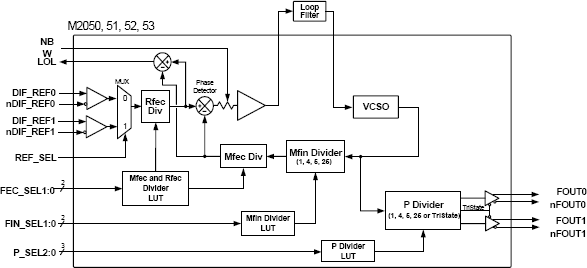

The M2050/51/52/53 is a VCSO (Voltage Controlled SAW Oscillator) based clock PLL designed for FEC clock ratio translation in 10Gb optical systems such as 10GbE 64b/66b. It supports both mapping and de-mapping of 64b/66b encoding and FEC (Forward Error Correction) clock multiplication ratios. The ratios are pin-selected from pre-programming look-up tables.

Documents

Technical documentation and resources

No documents available