EL7202CN

ObsoleteHIGH SPEED, DUAL CHANNEL POWER MOSFET DRIVERS

Deep-Dive with AI

Search across all available documentation for this part.

EL7202CN

ObsoleteHIGH SPEED, DUAL CHANNEL POWER MOSFET DRIVERS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | EL7202CN |

|---|---|

| Channel Type | Independent |

| Current - Peak Output (Source, Sink) [custom] | 2 A |

| Current - Peak Output (Source, Sink) [custom] | 2 A |

| Driven Configuration | Low-Side |

| Gate Type | N-Channel, P-Channel MOSFET |

| Input Type | Non-Inverting |

| Mounting Type | Through Hole |

| Number of Drivers | 2 |

| Operating Temperature [Max] | 125 ¯C |

| Operating Temperature [Min] | -40 °C |

| Package / Case | 0.3 in |

| Package / Case | 8-DIP |

| Package / Case | 7.62 mm |

| Rise / Fall Time (Typ) [custom] | 10 ns |

| Rise / Fall Time (Typ) [custom] | 7.5 ns |

| Supplier Device Package | 8-PDIP |

| Voltage - Supply [Max] | 15 V |

| Voltage - Supply [Min] | 4.5 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 71 | $ 4.26 | |

| 75 | $ 4.02 | |||

Description

General part information

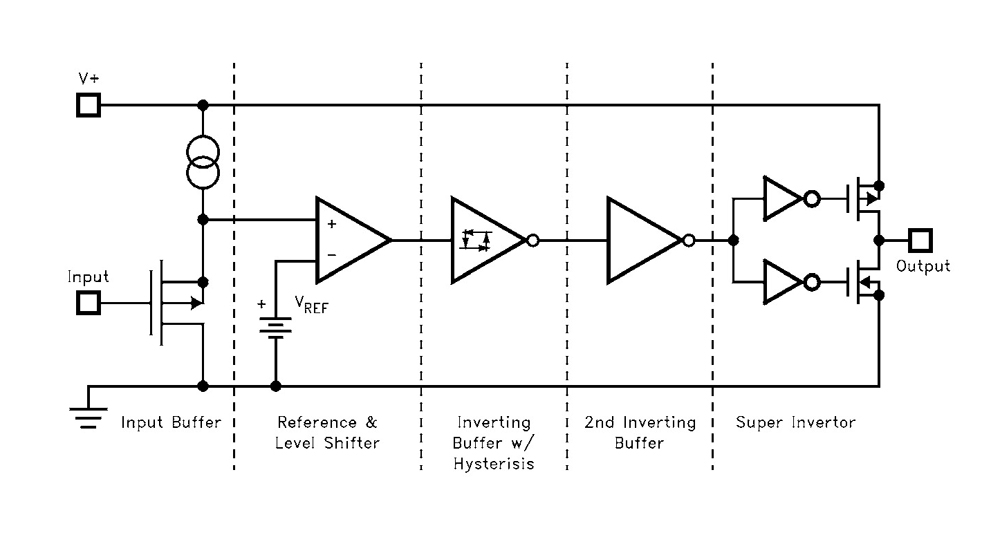

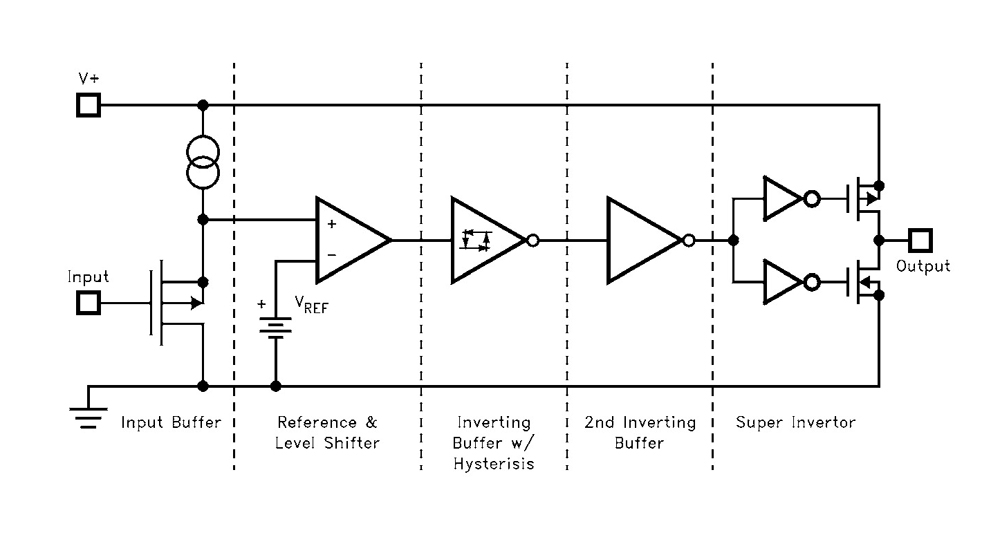

EL7202 Series

The EL7202, EL7212, EL7222 ICs are matched dual-drivers that improve the operation of the industry standard DS0026 clock drivers. The Elantec versions are very High-Speed drivers capable of delivering peak currents of 2. 0 amps into highly capacitive loads. The High-Speed performance is achieved by means of a proprietary Turbo-Driver circuit that speeds up input stages by tapping the wider voltage swing at the output. Improved speed and drive capability are enhanced by matched rise and fall delay times. These matched delays maintain the integrity of input-to-output pulse-widths to reduce timing errors and clock skew problems. This improved performance is accompanied by a 10 fold reduction in supply currents over bipolar drivers, yet without the delay time problems commonly associated with CMOS devices. Dynamic switching losses are minimized with non-overlapped drive techniques.

Documents

Technical documentation and resources