Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | CD40105BDMSR |

|---|---|

| Bus Directional | Uni-Directional |

| Current - Supply (Max) [Max] | 10 µA |

| Data Rate | 4 MHz |

| Expansion Type | Width, Depth |

| Function | Asynchronous |

| FWFT Support | False |

| Memory Size | 64 |

| Mounting Type | Through Hole |

| Operating Temperature [Max] | 125 °C |

| Operating Temperature [Min] | -55 °C |

| Package / Case | 7.62 mm, 0.3 in |

| Package / Case | 16-CDIP |

| Programmable Flags Support | False |

| Retransmit Capability | False |

| Supplier Device Package | 16-SBDIP |

| Voltage - Supply [Max] | 20 V |

| Voltage - Supply [Min] | 0 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

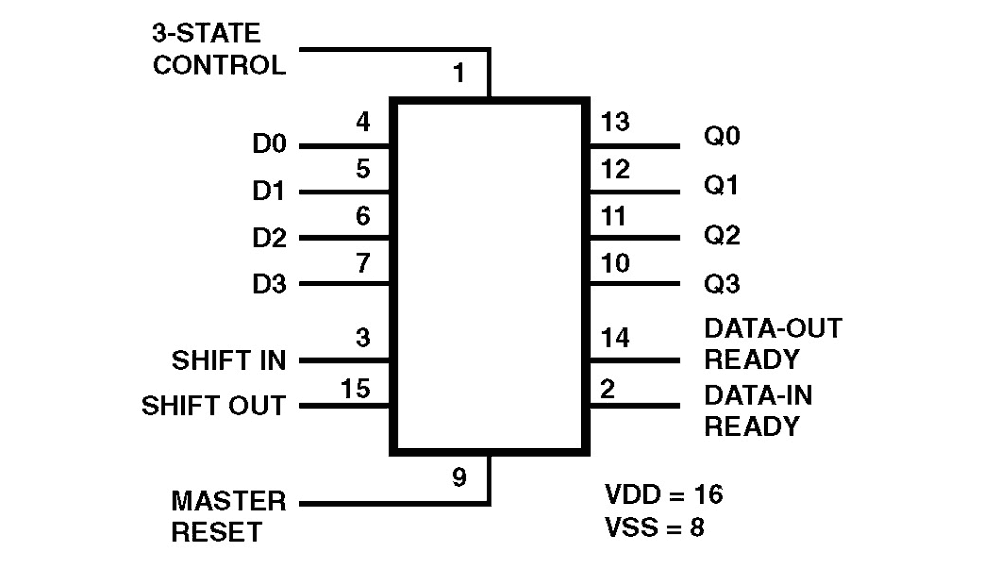

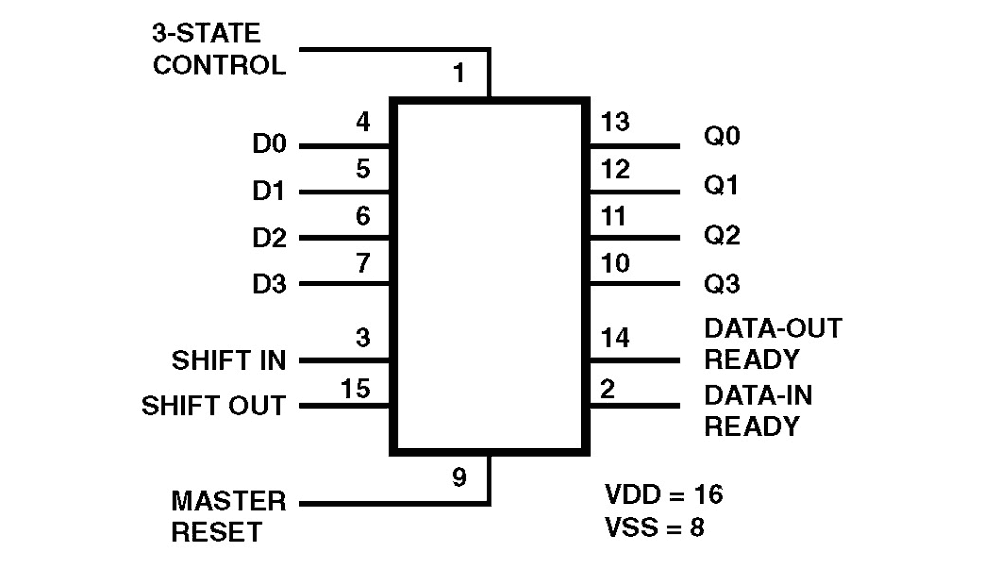

CD40105BMS Series

CD40105BMS is a low-power first-in-first-out (FIFO) elastic storage register that can store 16 4-bit words. It is capable of handling input and output data at different shifting rates. This feature makes it particularly useful as a buffer between asynchronous systems. Each word position in the register is clocked by a control flip-flop, which stores a marker bit. A 1 signifies that the position's data is filled and a 0 denotes a vacancy in that position. The control flip-flop detects the state of the preceding flip-flop and communicates its own status to the succeeding flip-flop. When a control flip-flop is in the 0 state and sees a 1 in the preceding flip-flop, it generates a clock pulse that transfers data from the preceding four data latches into its own four data latches and resets the preceding flip-flop to 0. The first and last control flip-flops have buffered outputs. Since all empty locations bubble automatically to the input end, and all valid data ripple through to the output end, the status of the first control flip-flop (DATA-IN READY) indicates if the FIFO is full, and the status of the last flip-flop (DATAOUT READY) indicates if the FIFO contains data. As the earliest data are removed from the bottom of the data stack (the output end), all data entered later will automatically propagate (ripple) toward the output.

Documents

Technical documentation and resources