8524AYLF

ObsoleteLOW SKEW,1-TO-22 DIFFERENTIAL-TO-HSTL FANOUT BUFFER

Deep-Dive with AI

Search across all available documentation for this part.

8524AYLF

ObsoleteLOW SKEW,1-TO-22 DIFFERENTIAL-TO-HSTL FANOUT BUFFER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 8524AYLF |

|---|---|

| Differential - Input:Output [custom] | True |

| Differential - Input:Output [custom] | True |

| Frequency - Max [Max] | 500 MHz |

| Input | HSTL, HCSL, CML, SSTL, LVPECL, LVDS, LVHSTL |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | 0 °C |

| Output | HSTL |

| Package / Case | 64-TQFP Exposed Pad |

| Ratio - Input:Output | 2:22 |

| Supplier Device Package | 64-TQFP-EP (10x10) |

| Type | Fanout Buffer (Distribution), Multiplexer |

| Voltage - Supply [Max] | 3.465 V |

| Voltage - Supply [Min] | 3.135 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 50 | $ 11.29 | |

Description

General part information

8524A Series

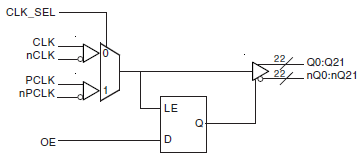

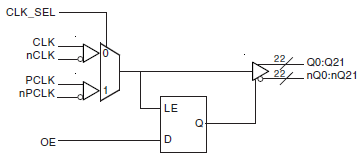

The 8524 is a low skew, 1-to-22 Differential-to-HSTL Fanout Buffer . The 8524 has two selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The device is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the OE pin. The 8524's low output and part-to-part skew characteristics make it ideal for workstation, server, and other high performance clock distribution applications.

Documents

Technical documentation and resources