8S89202BKILFT

ObsoleteLOW SKEW,2:1 LVPECL MUX WITH 1:8 FANOUT AND INTERNAL TERMINATION

Deep-Dive with AI

Search across all available documentation for this part.

8S89202BKILFT

ObsoleteLOW SKEW,2:1 LVPECL MUX WITH 1:8 FANOUT AND INTERNAL TERMINATION

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 8S89202BKILFT |

|---|---|

| Differential - Input:Output [custom] | True |

| Differential - Input:Output [custom] | True |

| Frequency - Max [Max] | 3 GHz |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVPECL |

| Ratio - Input:Output | 1:8 |

| Type | Divider |

| Voltage - Supply [Max] | 3.63 V, 2.625 V |

| Voltage - Supply [Min] | 2.97 V, 2.375 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

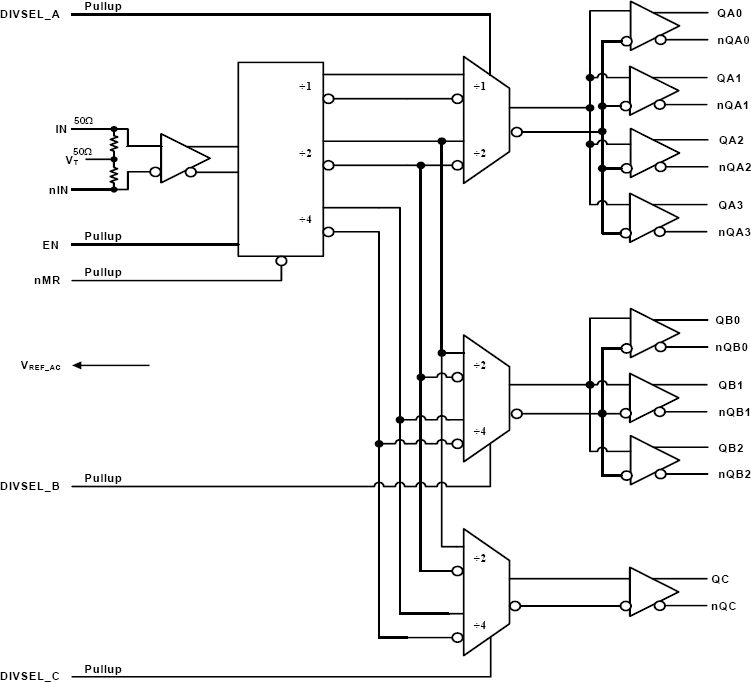

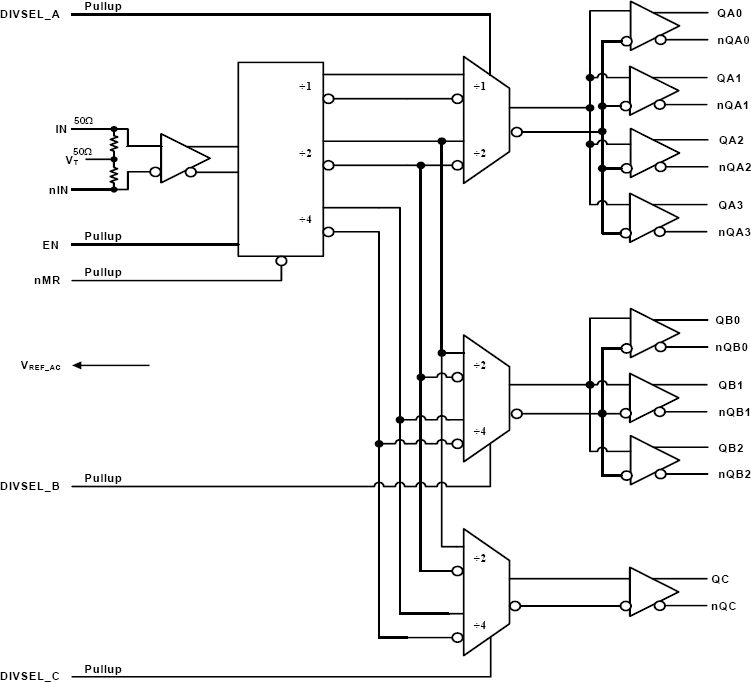

8S89202I Series

The 8S89202I is a high speed 1-to-8 Differential-to-LVPECL Clock Divider and is part of the high performance clock solutions from IDT. The 8S89202I is optimized for high speed and very low output skew, making it suitable for use in demanding applications such as SONET, 1 Gigabit and 10 Gigabit Ethernet, and Fibre Channel. The internally terminated differential inputs and VREF_AC pins allow other differential signal families such as LVPECL, LVDS and CML to be easily interfaced to the input with minimal use of external components. The device also has a selectable ÷1, ÷2, ÷4 output divider, which can allow the part to support multiple output frequencies from the same reference clock. The 8S89202I is packaged in a small 5mm x 5mm 32-pin VFQFN package which makes it ideal for use in space-constrained applications.

Documents

Technical documentation and resources