SN74SSTU32864NMJR

Active500-MHZ, 25-BIT CONFIGURABLE REGISTERED BUFFER WITH SSTL_18 INPUTS AND OUTPUTS

Deep-Dive with AI

Search across all available documentation for this part.

SN74SSTU32864NMJR

Active500-MHZ, 25-BIT CONFIGURABLE REGISTERED BUFFER WITH SSTL_18 INPUTS AND OUTPUTS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | SN74SSTU32864NMJR |

|---|---|

| Logic Type | Configurable Registered Buffer |

| Mounting Type | Surface Mount |

| Number of Bits | 14, 25 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

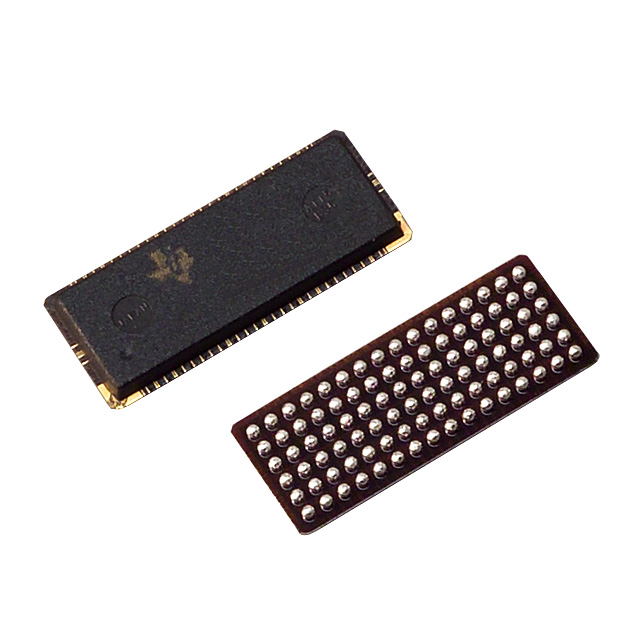

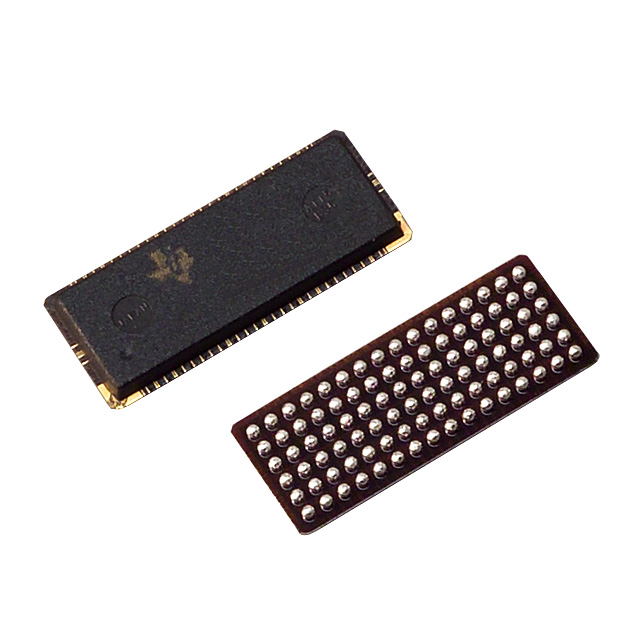

| Package / Case | 96-LFBGA |

| Supplier Device Package | 96-NFBGA (13.5x5.5) |

| Supply Voltage [Max] | 1.9 V |

| Supply Voltage [Min] | 1.7 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Cut Tape (CT) | 1 | $ 17.08 | |

| Digi-Reel® | 1 | $ 17.08 | ||

| Tape & Reel (TR) | 1000 | $ 10.82 | ||

| Texas Instruments | LARGE T&R | 1 | $ 13.37 | |

| 100 | $ 11.68 | |||

| 250 | $ 9.00 | |||

| 1000 | $ 8.05 | |||

Description

General part information

SN74SSTU32864 Series

This 25-bit 1:1 or 14-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCCoperation. In the 1:1 pinout configuration, only one device per DIMM is required to drive nine SDRAM loads. In the 1:2 pinout configuration, two devices per DIMM are required to drive 18 SDRAM loads.

All inputs are SSTL_18, except the LVCMOS reset (RESET)\ and LVCMOS control (Cn) inputs. All outputs are edge-controlled circuits optimized for unterminated DIMM loads and meet SSTL_18 specifications.

The SN74SSTU32864 operates from a differential clock (CLK and CLK\). Data are registered at the crossing of CLK going high and CLK\ going low.

Documents

Technical documentation and resources