Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | MPC9600AE |

|---|---|

| Differential - Input:Output | Yes/No |

| Frequency - Max [Max] | 200 MHz |

| Input | LVCMOS, LVPECL |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVCMOS |

| Package / Case | 48-LQFP |

| PLL | Yes with Bypass |

| Ratio - Input:Output | 2:21 |

| Supplier Device Package | 48-TQFP (7x7) |

| Type | PLL Clock Driver |

| Voltage - Supply [Max] | 3.465 V |

| Voltage - Supply [Min] | 2.375 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

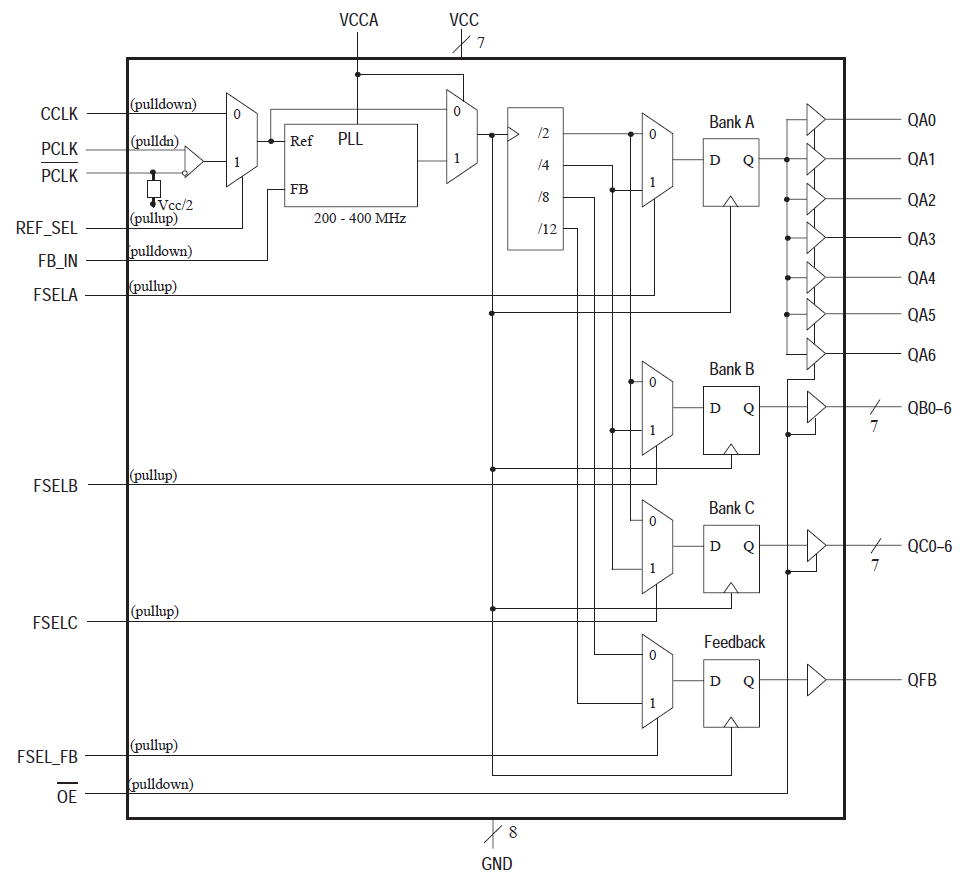

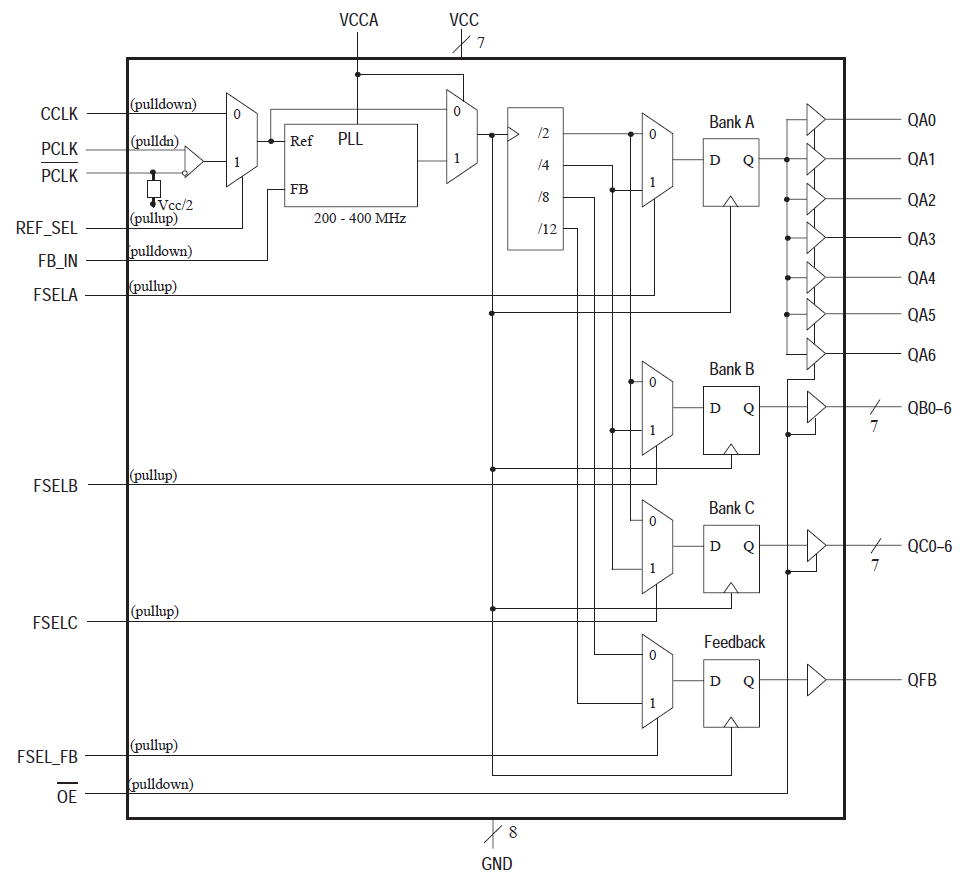

MPC9600 Series

The MPC9600 is a fully LVCMOS 2.5 V or 3.3 V compatible PLL clock driver. The MPC9600 has the capability to generate clock signals of 50 to 200 MHz from clock sources of 16.67 to 50 MHz. The internal PLL is optimized for this frequency range and does not require external loop filter components. QFB provides an output for the external feedback path to the feedback input FB_IN. The QFB divider ratio is configurable and determines the PLL frequency multiplication factor when QFB is directly connected to FB_IN. The MPC9600 is optimized for minimizing the propagation delay between the clock input and FB_IN. Three output banks of 7 outputs each bank can be individually configured to divide the VCO frequency by 2 or by 4. Combining the feedback and output divider ratios, the MPC9600 is capable to multiply the input frequency by 2, 3, 4, and 6. The reference clock is selectable either LVPECL or LVCMOS. The LVPECL reference clock feature allows the designer to use LVPECL fanout buffers for the inner branches of the clock distribution tree. All control inputs accept LVCMOS compatible levels. The outputs provide low impedance LVCMOS outputs capable of driving parallel terminated 50 ? transmission to VTT= VCC/2. For series terminated lines the MPC9600 can drive two lines per output giving the device an effective total fanout of 1:42. With guaranteed maximum output-to-output skew of 150 ps, the MPC9600 PLL clock driver meets the synchronization requirements of the most demanding systems. The VCCA analog power pin doubles as a PLL bypass select line for test purpose. When the VCCA is driven to GND the reference clock will bypass the PLL. The device is packaged in a 48-lead LQFP package to provide optimum combination of board density and performance.

Documents

Technical documentation and resources