810252DKI-02LF

ObsoleteVCXO JITTER ATTENUATOR & FEMTOCLOCK® MULTIPLIER

Deep-Dive with AI

Search across all available documentation for this part.

810252DKI-02LF

ObsoleteVCXO JITTER ATTENUATOR & FEMTOCLOCK® MULTIPLIER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 810252DKI-02LF |

|---|---|

| Differential - Input:Output | Yes/No |

| Divider/Multiplier | Yes/No |

| Frequency - Max [Max] | 312.5 MHz |

| Input | HCSL, LVPECL, SSTL, LVDS, LVHSTL |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVCMOS, LVTTL |

| Package / Case | 32-VFQFN Exposed Pad |

| PLL | True |

| Ratio - Input:Output [custom] | 2:2 |

| Supplier Device Package | 32-VFQFPN (5x5) |

| Type | Jitter Attenuator, Clock Multiplier |

| Voltage - Supply [Max] | 3.465 V |

| Voltage - Supply [Min] | 3.135 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tube | 40 | $ 15.27 | |

Description

General part information

810252DI-02 Series

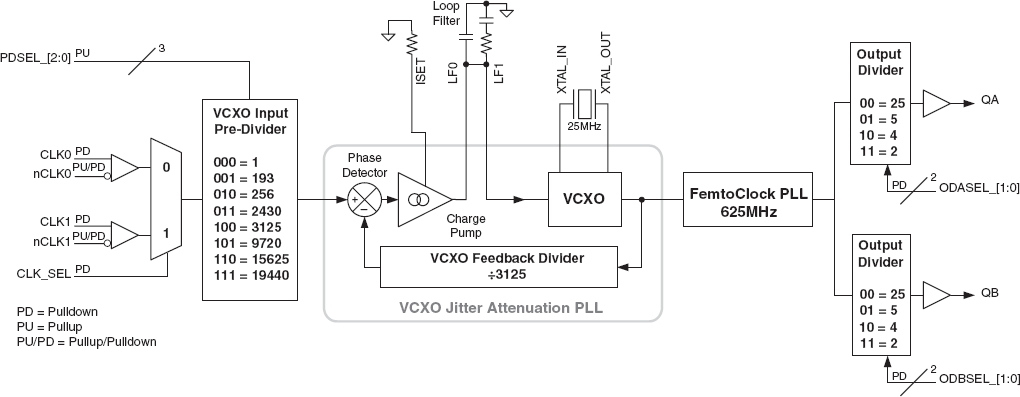

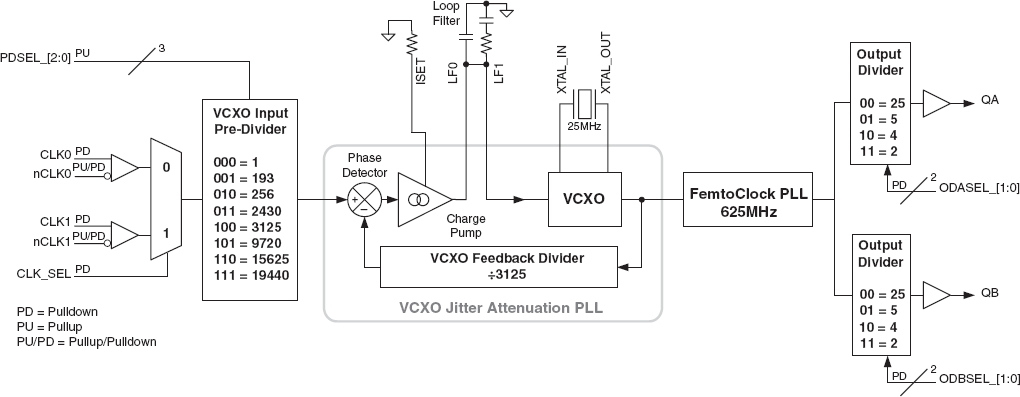

The 810252DI-02 is a PLL based synchronous multiplier that is optimized for PDH or SONET to Ethernet clock jitter attenuation and frequency translation. The device contains two internal frequency multiplication stages that are cascaded in series. The first stage is a VCXO PLL that is optimized to provide reference clock jitter attenuation. The second stage is a FemtoClock® frequency multiplier that provides the low jitter, high frequency Ethernet output clock that easily meets Gigabit and 10 Gigabit Ethernet jitter requirements. Pre-divider and output divider multiplication ratios are selected using device selection control pins. The multiplication ratios are optimized to support most common clock rates used in PDH, SONET and Ethernet applications. The VCXO requires the use of an external, inexpensive pullable crystal. The VCXO uses external passive loop filter components which allows configuration of the PLL loop bandwidth and damping characteristics. The device is packaged in a space-saving 32-VFQFN package and supports industrial temperature range.

Documents

Technical documentation and resources

No documents available