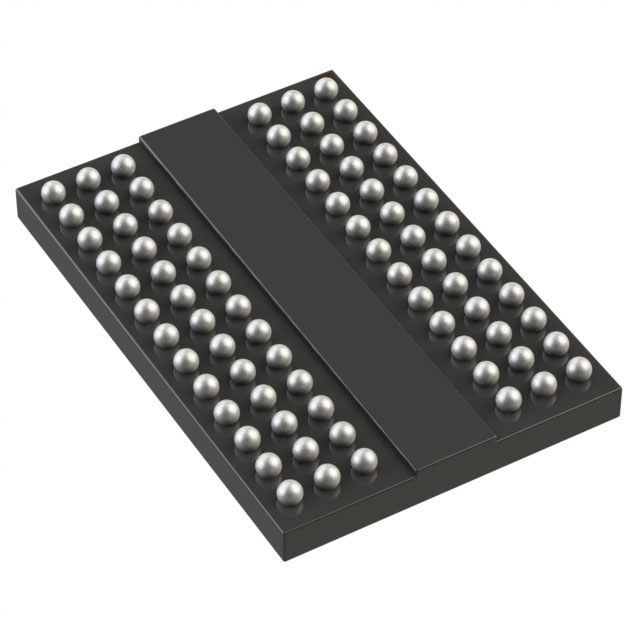

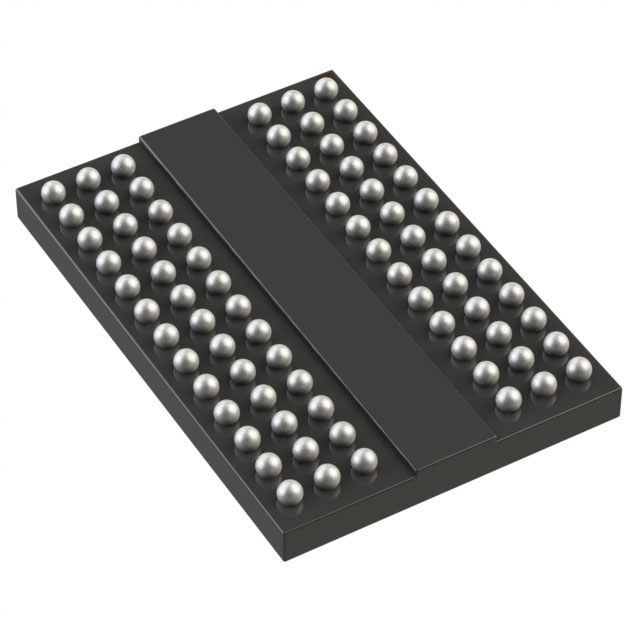

MT40A1G16TD-062E AIT:F

ActiveDRAM, AEC-Q100, DDR4, 16 GBIT, 1G X 16BIT, 1.6 GHZ, FBGA, 96 PINS

Deep-Dive with AI

Search across all available documentation for this part.

MT40A1G16TD-062E AIT:F

ActiveDRAM, AEC-Q100, DDR4, 16 GBIT, 1G X 16BIT, 1.6 GHZ, FBGA, 96 PINS

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | MT40A1G16TD-062E AIT:F |

|---|---|

| Access Time | 19 ns |

| Clock Frequency | 1600 MHz |

| Grade | Automotive |

| Memory Format | DRAM |

| Memory Interface | POD |

| Memory Organization | 1 G |

| Memory Type | Volatile |

| Operating Temperature [Max] | 95 °C |

| Operating Temperature [Min] | -40 °C |

| Qualification | AEC-Q100 |

| Technology | SDRAM - DDR4 |

| Write Cycle Time - Word, Page | 15 ns |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

Description

General part information

MT40A1G16 Series

MT40A1G16TD-062E AIT:F is a DDR4 SDRAM. It is a high-speed dynamic random-access memory internally configured as an eight-bank DRAM for the x16 configuration and as a 16-bank DRAM for the x4 and x8 configurations. The DDR4 SDRAM uses an 8n-prefetch architecture to achieve high-speed operation. The 8n-prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single READ or WRITE operation for the DDR4 SDRAM consists of a single 8n-bit wide, four-clock data transfer at the internal DRAM core and two corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

Documents

Technical documentation and resources