MK2069-01GILF

ObsoleteVCXO-BASED LINE CARD CLOCK SYNCHRONIZER

Deep-Dive with AI

Search across all available documentation for this part.

MK2069-01GILF

ObsoleteVCXO-BASED LINE CARD CLOCK SYNCHRONIZER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | MK2069-01GILF |

|---|---|

| Differential - Input:Output | False |

| Divider/Multiplier | Yes/No |

| Frequency - Max [Max] | 160 MHz |

| Input | LVCMOS |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVCMOS |

| Package / Case | 6.1 mm |

| Package / Case | 0.24 in |

| Package / Case | 56-TFSOP |

| PLL | True |

| Ratio - Input:Output [custom] | 3:3 |

| Supplier Device Package | 56-TSSOP |

| Voltage - Supply [Max] | 3.45 V |

| Voltage - Supply [Min] | 3.15 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Tube | 40 | $ 13.31 | |

Description

General part information

MK2069-01 Series

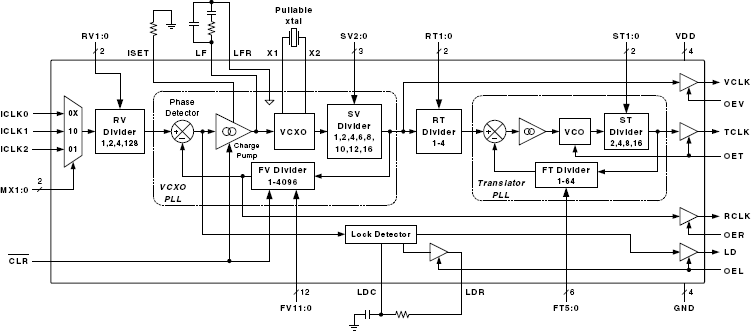

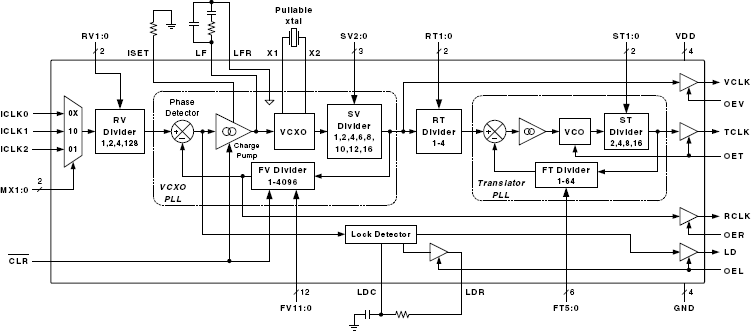

The MK2069-01 is a VCXO (Voltage Controlled Crystal Oscillator) based clock generator that offers system synchronization, jitter attenuation, and frequency multiplication or translation. It can accept an unstable, jittery input clock and provide a de-jittered, low phase noise output clock at a user determined frequency. The device's clock multiplication ratios are user selectable since all major PLL divider blocks can be configured through device pin settings. External PLL loop filter components allow tailoring of the VCXO PLL loop response and therefore the clock jitter attenuation characteristics. The MK2069-01 is ideal for line card applications. Its three input MUX enables selection of the master or slave (backup) system clocks, as well as a backup local line card clock. The lock detector (LD) output serves as a clock status monitor. The clear (CLR) input enables rapid synchronization to the phase of a newly selected input clock, while eliminating the generation of extra clock cycles and wander caused by memory in the PLL feedback divider. CLR also serves as a temporary holdover function when kept low.

Documents

Technical documentation and resources