Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

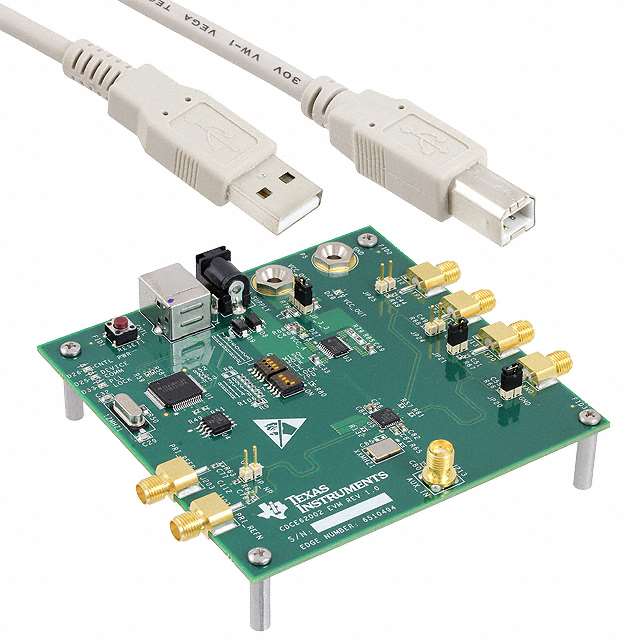

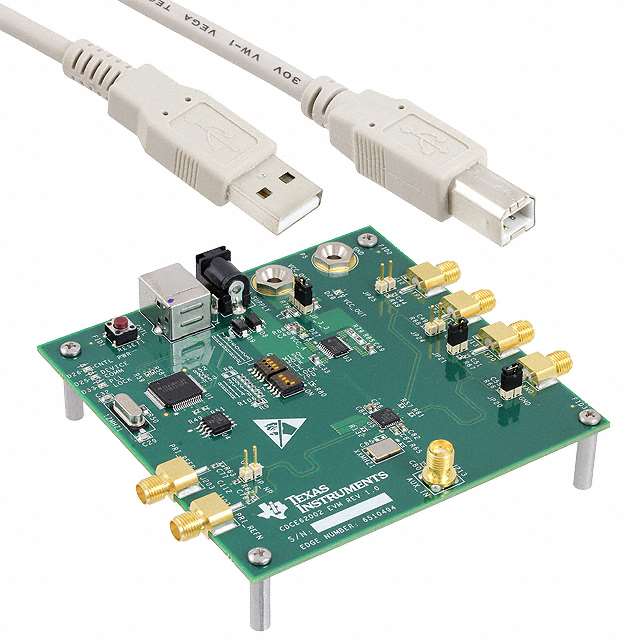

| Specification | CDCE62002EVM |

|---|---|

| Function | Clock Generator |

| Supplied Contents | Board(s) |

| Type | Timing |

| Utilized IC / Part | CDCE62002 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 238.80 | |

Description

General part information

CDCE62002 Series

The CDCE62002 device is a high-performance clock generator featuring low output jitter, a high degree of configurability through a SPI interface, and programmable start-up modes determined by on-chip EEPROM. Specifically tailored for clocking data converters and high-speed digital signals, the CDCE62002 achieves jitter performance under 0.5 ps RMS(1).

It incorporates a synthesizer block with partially integrated loop filter, a clock distribution block including programmable output formats, and an input block featuring an innovative smart multiplexer. The clock distribution block includes two individually programmable outputs that can be configured to provide different combinations of output formats (LVPECL, LVDS, LVCMOS). Each output can also be programmed to a unique output frequency (ranging from 10.94 MHz to 1.175 GHz(2)). If Both outputs are configured in single-ended mode (such as LVCMOS), the CDCE62002 supports up to four outputs. The input block includes one universal differential inputs which support frequencies up to 500 MHz and an auxiliary input that can be configured to connect to an external AT-Cut crystal through an onboard oscillator block. The smart input multiplexer has two modes of operation, manual and automatic. In manual mode, the user selects the synthesizer reference through the SPI interface. In automatic mode, the input multiplexer will automatically select between the highest priority input clock available.

(1)10-kHz to 20-MHz integration bandwidth.(2)Frequency range depends on operational mode and output format selected.

Documents

Technical documentation and resources