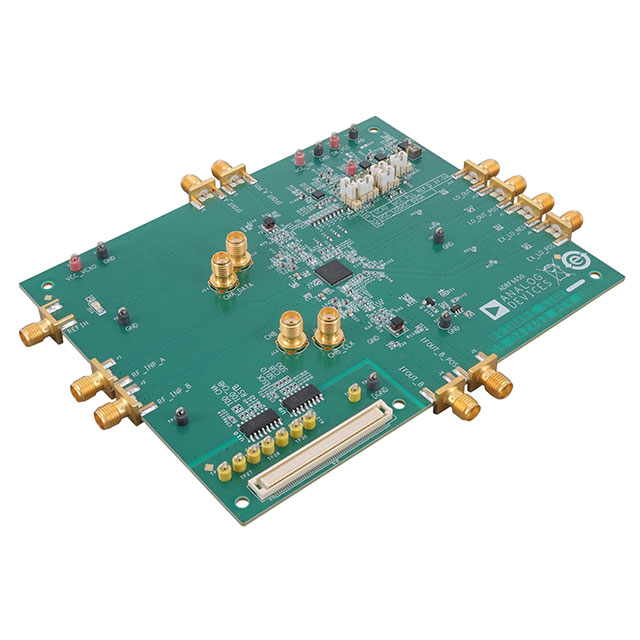

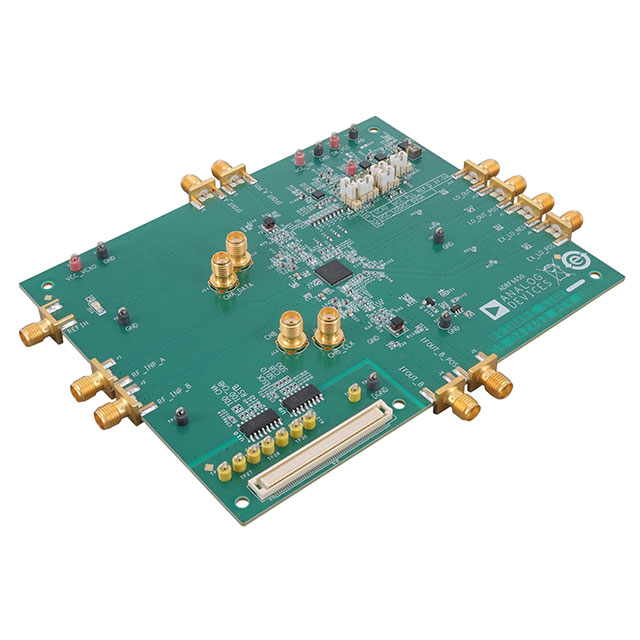

ADRF6650-EVALZ

ActiveADRF6650 EVAL BOARD

Deep-Dive with AI

Search across all available documentation for this part.

ADRF6650-EVALZ

ActiveADRF6650 EVAL BOARD

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | ADRF6650-EVALZ |

|---|---|

| Contents | Board |

| For Use With/Related Products | ADRF6650 |

| Frequency (Max) | 2.7 GHz |

| Frequency (Min) | 450 MHz |

| Supplied Contents | Board(s) |

| Type | Downconverter |

| Utilized IC / Part | ADRF6650 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | Updated |

|---|---|---|---|---|

| Digikey | Box | 1 | $ 195.79 | 1m+ |

| N/A | 2 | $ 196.35 | 1m+ | |

CAD

3D models and CAD resources for this part

Description

General part information

ADRF6650 Series

The ADRF6650 is a highly integrated downconverter that integrates dual mixers, dual digital switched attenuators, dual digital variable gain amplifiers, a phase-locked loop (PLL), and voltage controlled oscillators (VCOs). In addition, the ADRF6650 integrates two radio frequency (RF) baluns, serial gain control (SGC) controls, and fast enable inputs for time division duplex (TDD) operation.The on-chip RF baluns enable the ADRF6650 to support 50 Ω terminated RF inputs. The integrated passive mixer provides a highly linear downconversion for a 200 MHz, sliding, intermediate frequency (IF) window. The ADRF6650 uses broadband square wave limiting local oscillator (LO) amplifiers to achieve an RF bandwidth of 450 MHz to 2700 MHz. Unlike conventional narrow-band sine wave LO amplifier solutions, this amplifier permits the LO to be applied either above or below the RF input over an extremely wide bandwidth.The ADRF6650 offers two alternatives for generating the differential LO input signal: internally via the on-chip fractional-N synthesizer with low phase noise VCOs, or externally via a low phase noise LO signal. The integrated PLL/VCO enables continuous LO coverage from 450 MHz to 2900 MHz. The PLL reference input supports a wide frequency range and includes integrated reference dividers before the phase frequency detector (PFD).The ADRF6650 is fabricated using an advanced silicon-germanium (SiGe) bipolar complementary metal-oxide semiconductor (BiCMOS) process. It is available in a 56-lead, RoHS-compliant, 8 mm × 8 mm, lead frame chip scale package (LFCSP) package with an exposed pad. Performance is specified over the −40°C to +105°C maximum paddle temperature.ApplicationsMultiband/multistandard cellular base station diversity receiversWideband radio link diversity downconvertersMultimode cellular extenders and picocells

Documents

Technical documentation and resources