601M-01LFT

ObsoleteLOW PHASE NOISE CLOCK MULTIPLIER

Deep-Dive with AI

Search across all available documentation for this part.

601M-01LFT

ObsoleteLOW PHASE NOISE CLOCK MULTIPLIER

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 601M-01LFT |

|---|---|

| Differential - Input:Output [custom] | False |

| Differential - Input:Output [custom] | False |

| Frequency - Max [Max] | 156 MHz |

| Input | Crystal, Clock |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 70 °C |

| Operating Temperature [Min] | 0 °C |

| Output | CMOS |

| Package / Case | 16-SOIC |

| Package / Case | 0.154 in, 3.9 mm |

| PLL | True |

| Ratio - Input:Output [custom] | 2 |

| Ratio - Input:Output [custom] | 2 |

| Supplier Device Package | 16-SOIC |

| Voltage - Supply [Max] | 5.5 V |

| Voltage - Supply [Min] | 3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | N/A | 0 | $ 0.00 | |

Description

General part information

601-01 Series

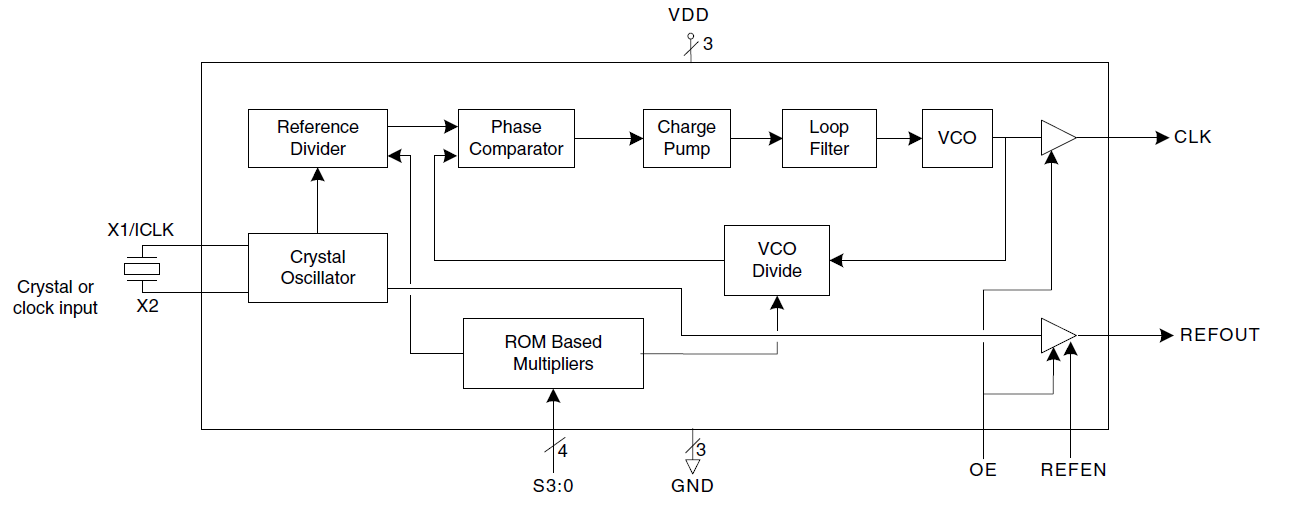

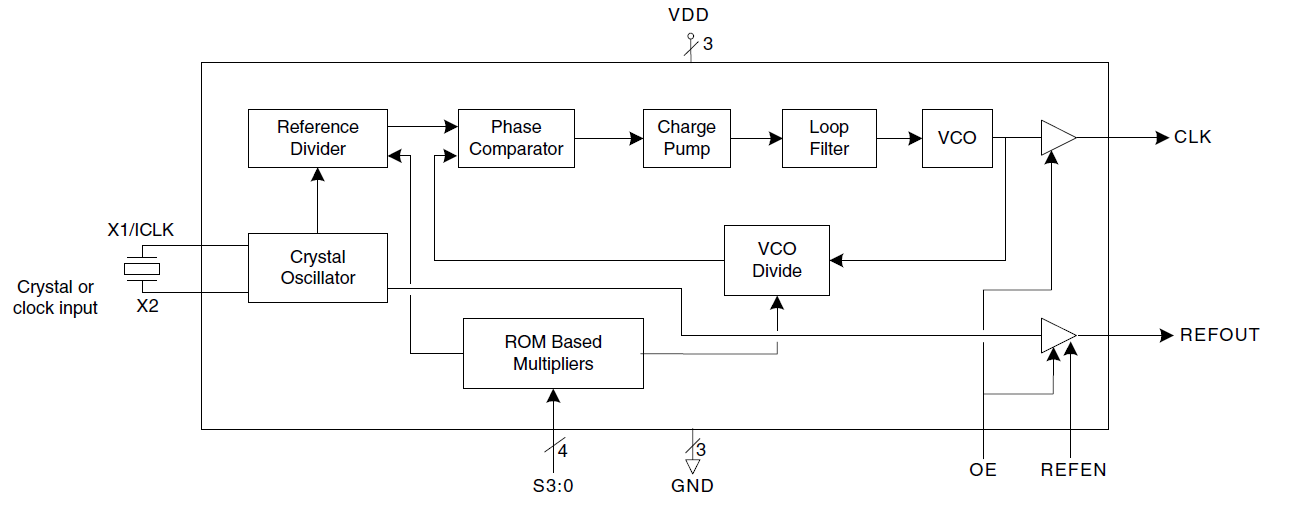

The ICS601-01 is a low-cost, low phase noise, high-performance clock synthesizer for applications which require low phase noise and low jitter. It is Renesas’ lowest phase noise multiplier, and also the lowest CMOS part in the industry. Using Renesas’ patented analog and digital Phase-Locked Loop (PLL) techniques, the chip accepts a 10 - 27 MHz crystal or clock input, and produces output clocks up to 156 MHz at 3.3 V. This product is intended for clock generation. It has low output jitter (variation in the output period), but input to output skew and jitter are not defined nor guaranteed. For applications which require defined input to output timing, use the ICS670-01.

Documents

Technical documentation and resources