870919BRILF

ObsoleteIC CLOCK GENERATOR 28QSOP

Deep-Dive with AI

Search across all available documentation for this part.

870919BRILF

ObsoleteIC CLOCK GENERATOR 28QSOP

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 870919BRILF |

|---|---|

| Differential - Input:Output | False |

| Divider/Multiplier | Yes/No |

| Frequency - Max [Max] | 160 MHz |

| Input | LVCMOS |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVCMOS |

| Package / Case | 28-SSOP |

| PLL | Yes with Bypass |

| Ratio - Input:Output [custom] | 8 |

| Ratio - Input:Output [custom] | 2 |

| Type | Clock Generator |

| Voltage - Supply | 3.3 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

870919I Series

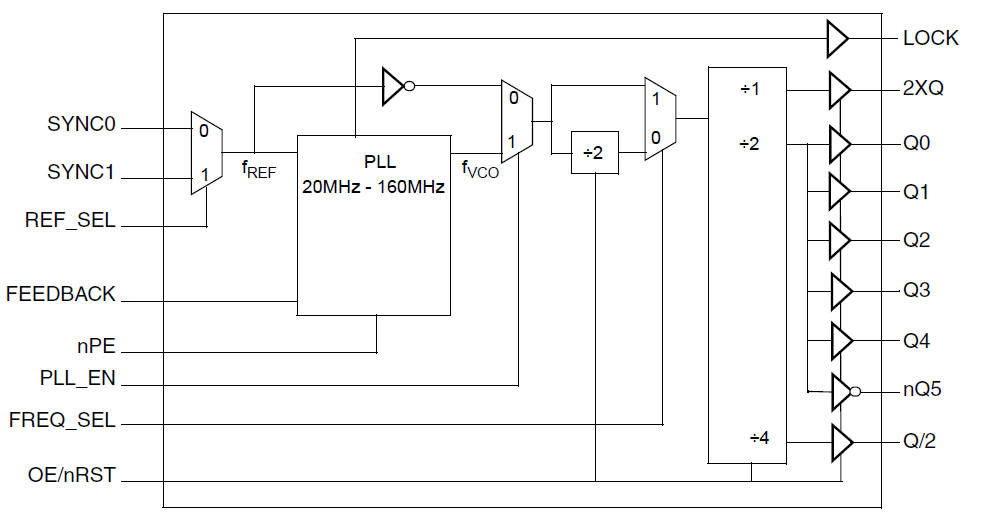

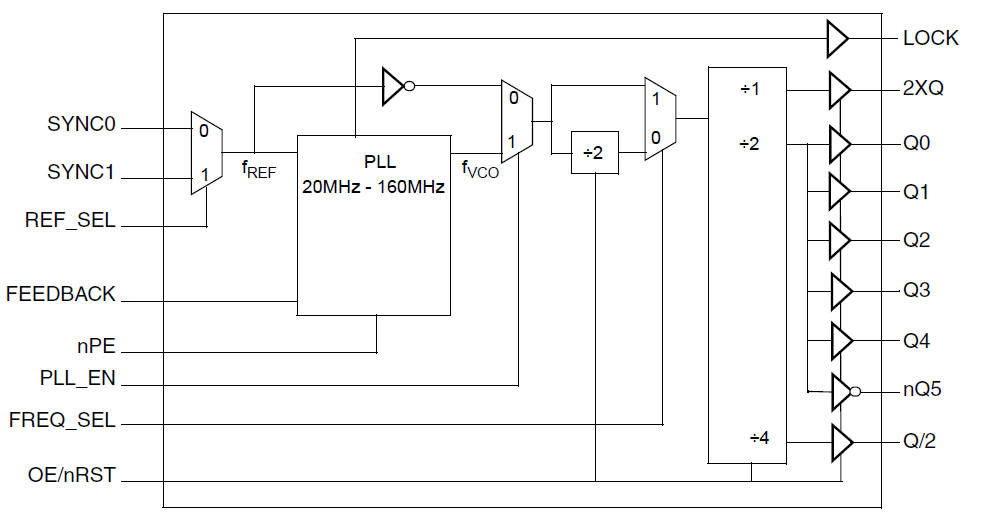

The 870919I is an LVCMOS clock generator that uses an internal phase lock loop (PLL) for frequency multiplication and to lock the low-skew outputs to the selected reference clock. The device offers eight outputs. The PLL loop filter is completely internal and does not require external components. Several output configurations of the PLL feedback and a divide-by-2 (controlled by FREQ_SEL) allow applications to optimize frequency generation over a wide range of input reference frequencies. The PLL can also be disabled by the PLL_EN control signal to allow for low frequency or DC testing. The LOCK output asserts to indicate when phase-lock has been achieved. The 870919I device is a member of the HiperClocks family of high performance clock solutions from IDT.

Documents

Technical documentation and resources