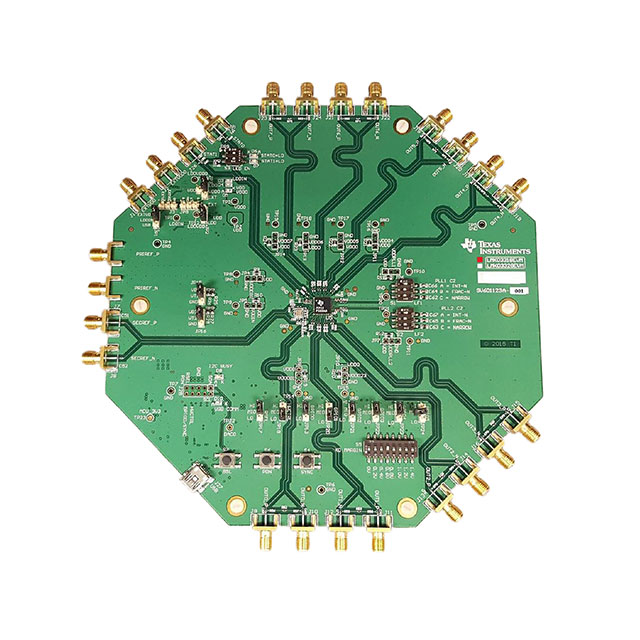

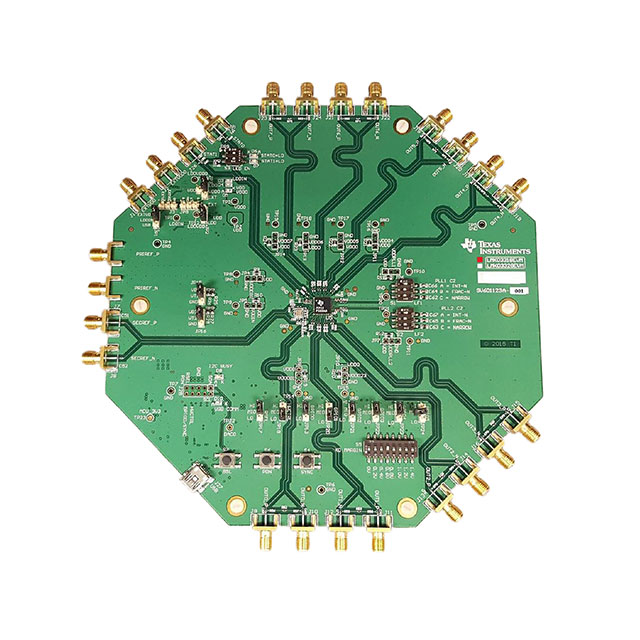

LMK03318EVM

ActiveLMK03318EVM ULTRA-LOW-JITTER CLO

Deep-Dive with AI

Search across all available documentation for this part.

LMK03318EVM

ActiveLMK03318EVM ULTRA-LOW-JITTER CLO

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | LMK03318EVM |

|---|---|

| Contents | Cable(s), Board(s) |

| Function | Clock Generator |

| Secondary Attributes | Graphical User Interface (GUI) |

| Supplied Contents | Cable(s), Board(s) |

| Type | Timing |

| Utilized IC / Part | LMK03318 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 1 | $ 358.80 | |

Description

General part information

LMK03318 Series

The LMK03318 device is an ultra-low-noise PLLATINUM™ clock generator with one fractional-N frequency synthesizer with integrated VCO, flexible clock distribution and fanout, and pin-selectable configuration states stored in on-chip EEPROM. The device can generate multiple clocks for various multi-gigabit serial interfaces and digital devices, thus reducing BOM cost and board area and improving reliability by replacing multiple oscillators and clock distribution devices. The ultra-low jitter reduces bit-error rate (BER) in high-speed serial links.

For the PLL, a differential clock, a single-ended clock, or a crystal input can be selected as the reference clock. The selected reference input can be used to lock the VCO frequency at an integer or fractional multiple of the reference input frequency. The VCO frequency can be tuned between 4.8 GHz and 5.4 GHz. The PLL offers the flexibility to select a predefined or user-defined loop bandwidth, depending on the needs of the application. The PLL has a post-divider that can be selected between divide-by 2, 3, 4, 5, 6, 7, or 8.

All the output channels can select the divided-down VCO clock from the PLL as the source for the output divider to set the final output frequency. Some output channels can also independently select the reference input for the PLL as an alternative source to be bypassed to the corresponding output buffers. The 8-bit output dividers support a divide range of 1 to 256 (even or odd), output frequencies up to 1 GHz, and output phase synchronization capability.

Documents

Technical documentation and resources