Deep-Dive with AI

Search across all available documentation for this part.

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

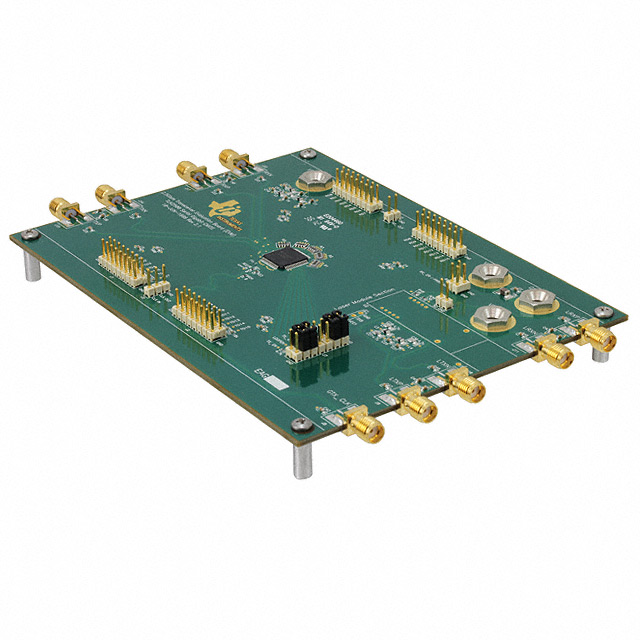

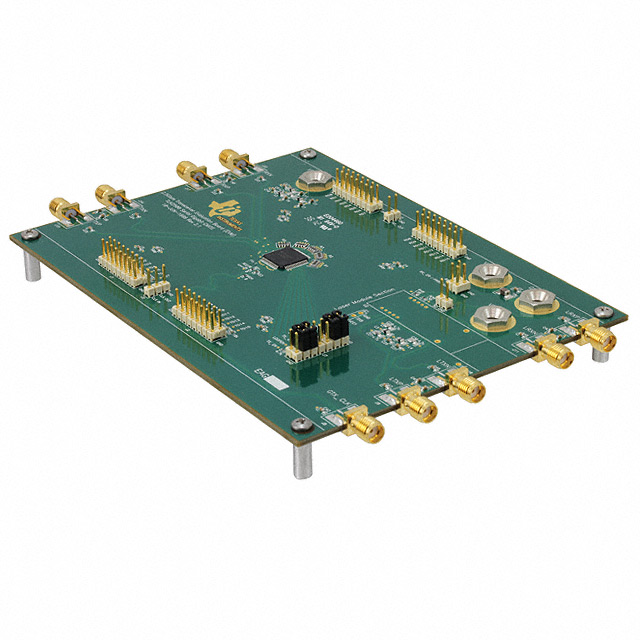

| Specification | TLK2501EVM |

|---|---|

| Function | Serializer, Deserializer (SerDes) |

| Supplied Contents | Board(s) |

| Type | Interface |

| Utilized IC / Part | TLK2501 |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

| Digikey | Bulk | 1 | $ 958.80 | |

Description

General part information

TLK2501 Series

The TLK2501 is a member of the transceiver family of multigigabit transceivers used in ultrahigh-speed bidirectional point-to-point data transmission systems. The TLK2501 supports an effective serial interface speed of 1.5 Gbps to 2.5 Gbps, providing up to 2 Gbps of data bandwidth. The TLK2501 is pin-for-pin compatible with the TLK2500. The TLK2501 is both pin-for-pin compatible with and functionally identical to the TLK1501, a 0.6 to 1.5 Gbps transceiver, and the TLK3101, a 2.5 to 3.125 Gbps transceiver, providing a wide range of performance solutions with no required board layout changes.

The primary application of this chip is to provide very high-speed I/O data channels for point-to-point baseband data transmission over controlled impedance media of approximately 50. The transmission media can be printed-circuit board, copper cables, or fiber-optic cable. The maximum rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

This device can also be used to replace parallel data transmission architectures by providing a reduction in the number of traces, connector terminals, and transmit/receive terminals. Parallel data loaded into the transmitter is delivered to the receiver over a serial channel, which can be a coaxial copper cable, a controlled impedance backplane, or an optical link. It is then reconstructed into its original parallel format. It offers significant power and cost savings over current solutions, as well as scalability for higher data rate in the future.

Documents

Technical documentation and resources