87973DYILF

Obsolete1:12 LVCMOS CLOCK GENERATOR

Deep-Dive with AI

Search across all available documentation for this part.

87973DYILF

Obsolete1:12 LVCMOS CLOCK GENERATOR

Deep-Dive with AI

Technical Specifications

Parameters and characteristics for this part

| Specification | 87973DYILF |

|---|---|

| Differential - Input:Output | Yes/No |

| Divider/Multiplier | Yes/No |

| Frequency - Max [Max] | 125 MHz |

| Input | LVDS, LVHSTL, LVCMOS, LVPECL, LVTTL, HCSL, SSTL |

| Mounting Type | Surface Mount |

| Number of Circuits | 1 |

| Operating Temperature [Max] | 85 °C |

| Operating Temperature [Min] | -40 °C |

| Output | LVCMOS, LVTTL |

| Package / Case | 52-LQFP |

| PLL | Yes with Bypass |

| Ratio - Input:Output | 4, 12 |

| Supplier Device Package | 52-TQFP (10x10) |

| Type | Zero Delay Buffer, Clock Multiplier |

| Voltage - Supply [Max] | 3.465 V |

| Voltage - Supply [Min] | 3.135 V |

Pricing

Prices provided here are for design reference only. For realtime values and availability, please visit the distributors directly

| Distributor | Package | Quantity | $ | |

|---|---|---|---|---|

Description

General part information

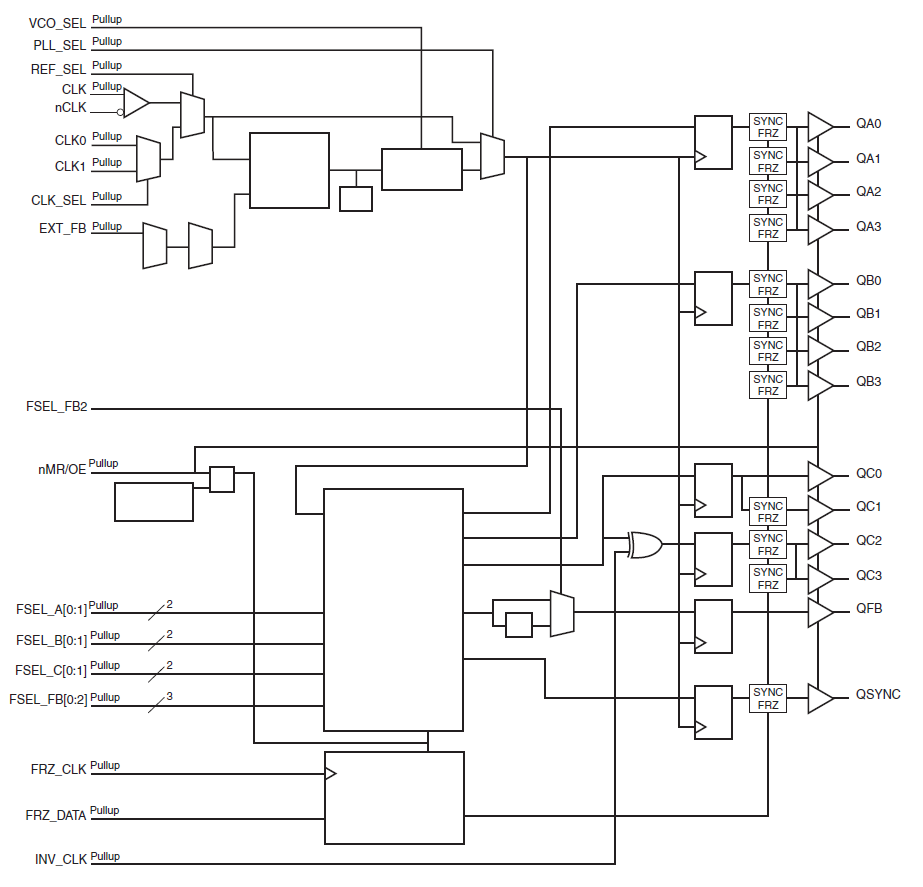

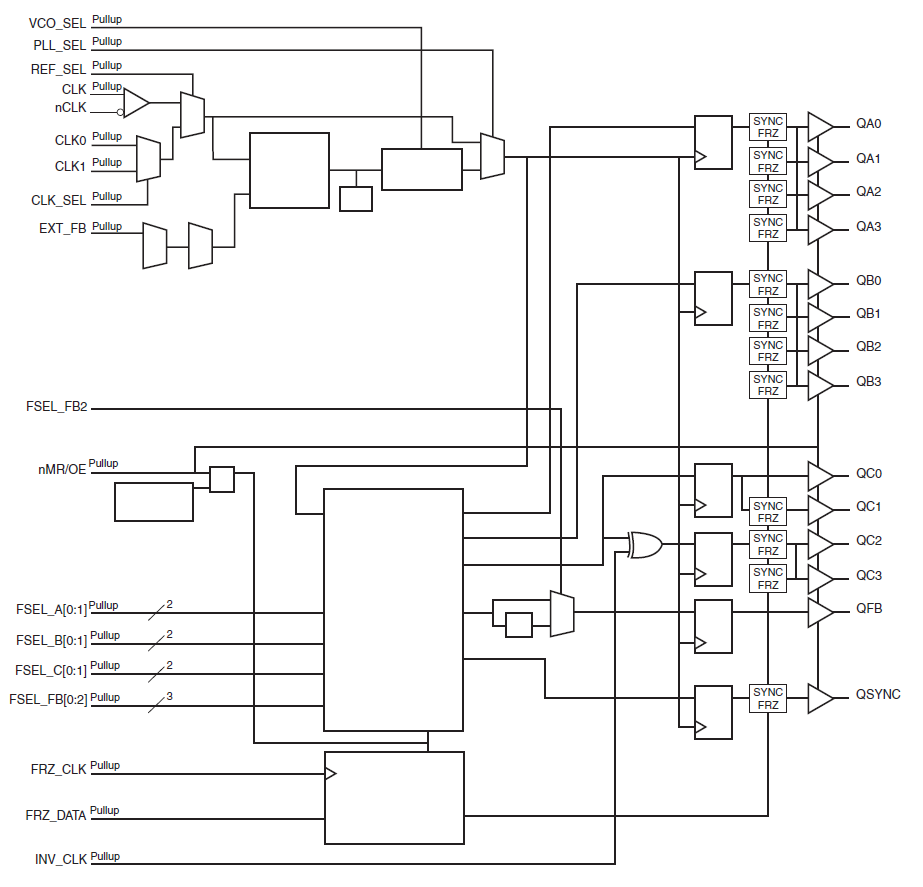

87973I Series

The 87973I is a LVCMOS/LVTTL clock generator from IDT. The 87973I has three selectable inputs and provides fourteen LVCMOS/LVTTL outputs. The 87973I is a highly flexible device. The three selectable inputs (1 differential and 2 single ended inputs) are often used in systems requiring redundant clock sources. Up to three different output frequencies can be generated among the three output banks. The three output banks and feedback output each have their own output dividers which allows the device to generate a multitude of different bank frequency ratios and output-to-input frequency ratios. In addition, 2 outputs in Bank C (QC2, QC3) can be selected to be inverting or non-inverting. The output frequency range is 8.33MHz to125MHz. The input frequency range is 5MHz to 120MHz. The 87973I also has a QSYNC output which can by used for system synchronization purposes. It monitors Bank A and Bank C outputs and goes low one period prior to coincident rising edges of Bank A and Bank C clocks. QSYNC then goes high again when the coincident rising edges of Bank A and Bank C occur. This feature is used primarily in applications where Bank A and Bank C are running at different frequencies, and is particularly useful when they are running at non-integer multiples of one another.

Documents

Technical documentation and resources